Intel

®

EP80579 Integrated Processor Product Line May 2010

Order Number: 320068-005US 242

Local Expansion Bus (LEB) Interface—Intel

®

EP80579 Integrated Processor Product Line

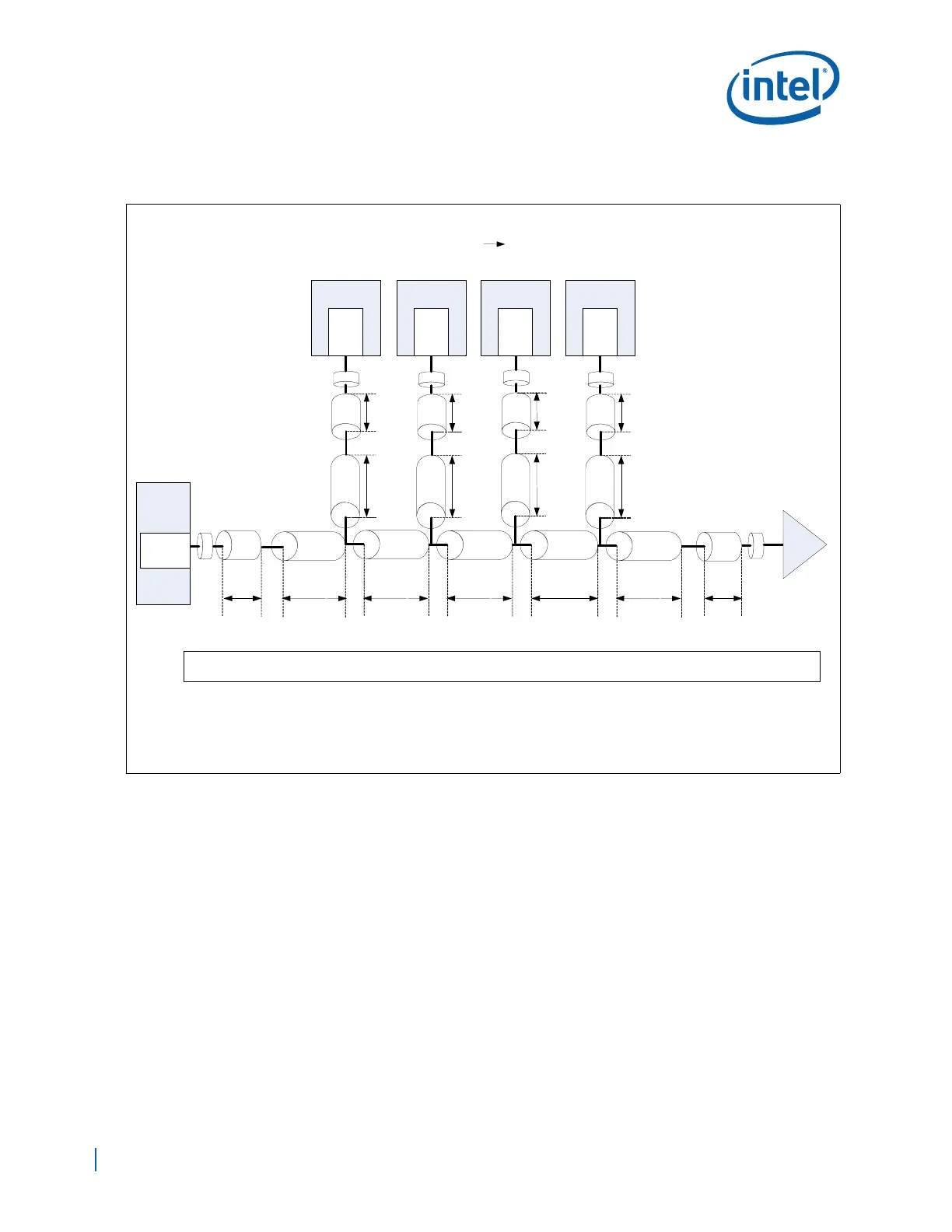

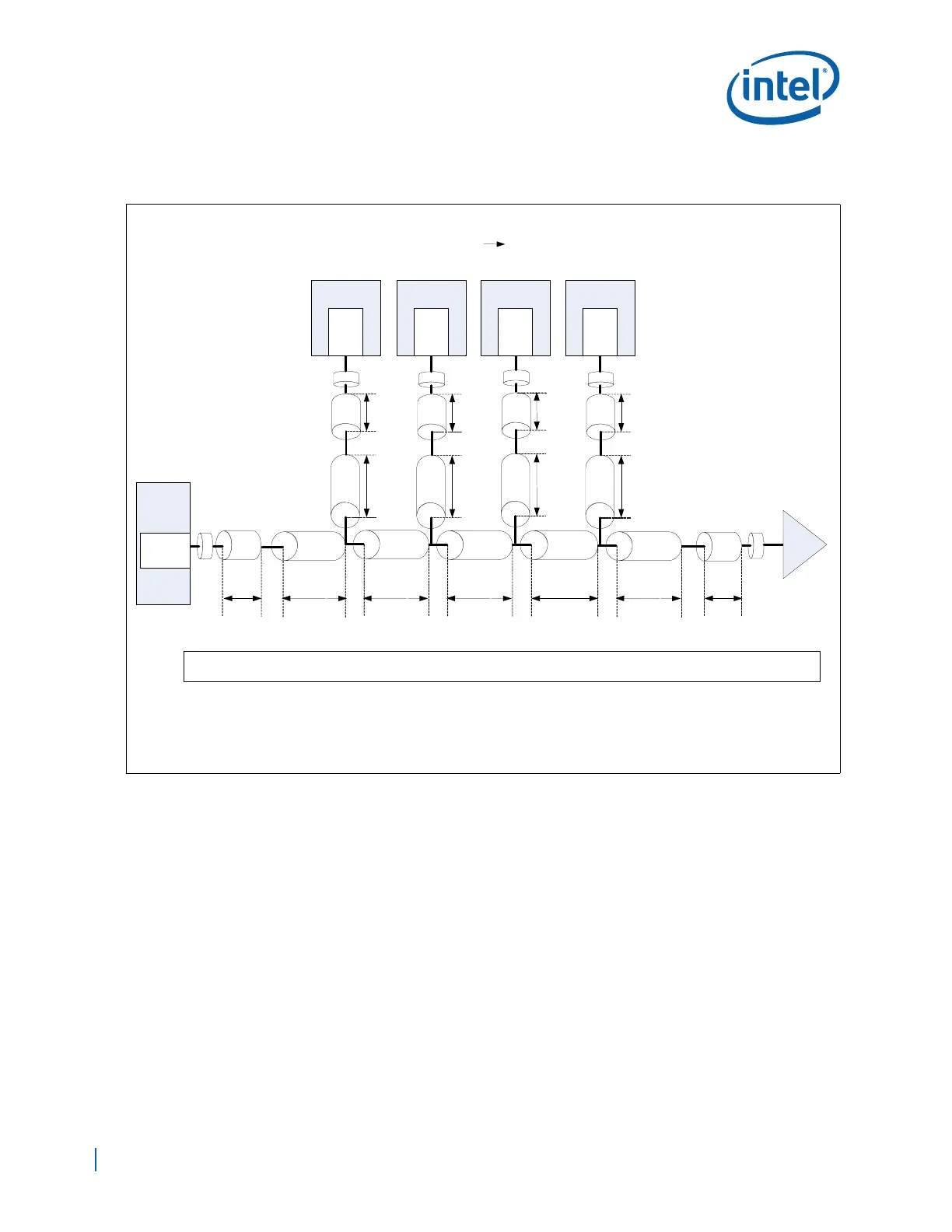

22.3.4 Data and Control Star Topology

Data and control signals require very similar guidelines as stated in the above Section

22.3.3, “Address Star Topologies” on page 241, but with a very important key

difference, it is required to place a series 22 ohm damping resistor at the destination

end of the transmission line. This will help damp the over shoot of signals when the

data logic levels are generated by the peripherals. The overshoot can be generated

when reading the devices and the signals are propagated on the bus. Match signals

groups as stated in the above section to approximately 500 mils.

Figure 149 shows the star topology used in the Development Board design to

interconnect the data and control signals to the various peripherals in the LEB bus.

Table 90 provides the general routing rules such as impedance, min and max trace

lengths.

22.3.4.1 Adding Delay to EX_RD#

The EP80579 requires a 2nSec (min) read hold time (Trdhold) on the data bus when

reading external devices connecting to the LEB interface. Some of the external devices

are able to meet the requirement but many of them do not.

Figure 148. Address Signals Star Topology Diagram

Via Break out Break in

ADDR

BUFFER

EP80579

LADDR_Brk_out LADDR_TL1_route LADDR_Brk_in

LADDR_Brk_out + LADDR_TL1_route + LADDR_Brk_inLADDR_Total =

NOTE: Breakout\ Breakin descriptions are as follows:

1. Routing where trace is 4 mil wide and 4mil spacing is implemented to escape\ enter BGA

2. The Breakout \ Breakin Length is defined from the pin of the BGA, to where 4 mil spacing

increases to the required spacing per SI recommendations.

a). CS = 10 mil edge-to-edged (e2e) for Stripline

b). CS = 12 mil edge-to-edge (e2e) for Microstrip

Via

Address Star Topology

(EP80579 Peripheral)

TL1

LADDR_TL3_route

TL3

TL2

TL2 TL2

TL2

Break in

LADDR_Brk_in

ADDR

Via

TL3

Break in

LADDR_Brk_in

ADDR

Via

TL3

Break in

LADDR_Brk_in

ADDR

Via

TL3

Break in

LADDR_Brk_in

ADDR

Via

LADDR_TL2_route LADDR_TL2_route LADDR_TL2_route LADDR_TL2_route

LADDR_TL3_route

LADDR_TL3_route

LADDR_TL3_route

FPGA

COMPACT

FLASH

STRATA

FLASH #2

4XLADDR_TL2_route +

ADDR

STRATA

FLASH #1

Loading...

Loading...