Intel

®

EP80579 Integrated Processor Product Line—Platform System Clock

Intel

®

EP80579 Integrated Processor Product Line

Platform Design Guide May 2010

105 Order Number: 320068-005US

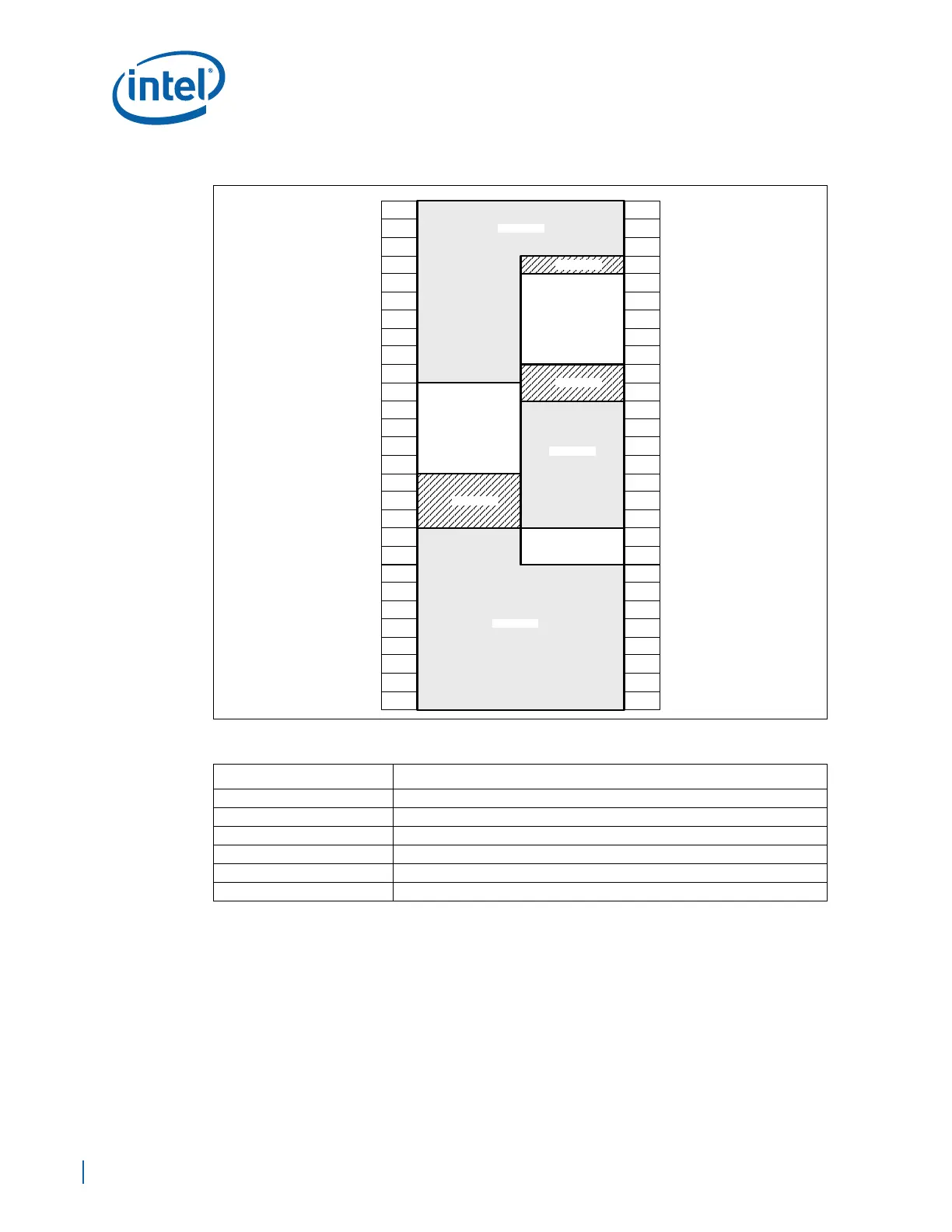

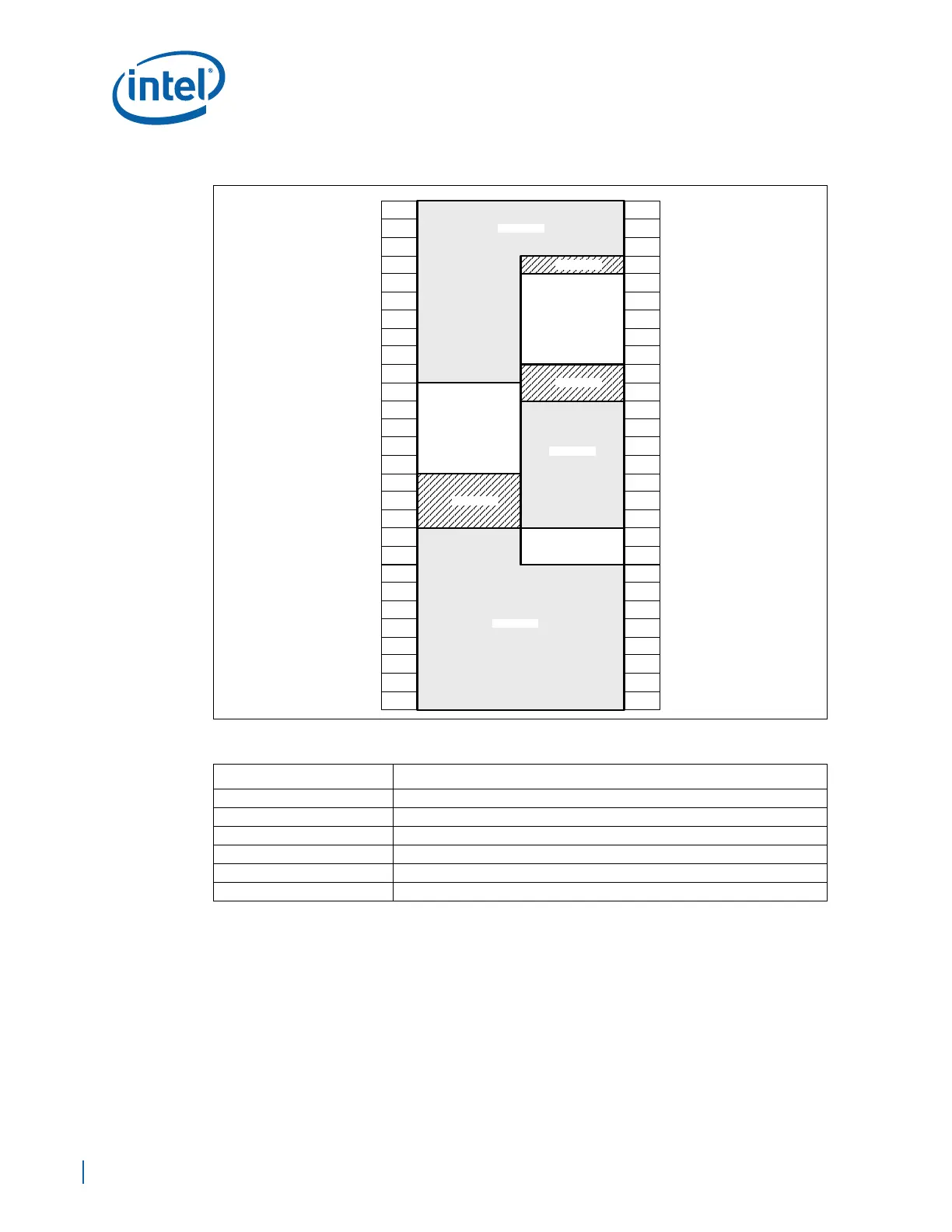

Figure 67 shows the CK410 decoupling capacitors and ferrite beads that are associated

with the different clock output groupings:

Figure 66. Clock Power Groupings for Decoupling / Filtering

Table 25. Clock Grouping for Decoupling / Filtering

Clock Group Signals in Group

Analog VDD_A, VSS_A

SRC SRC[7:1], SRC[7:1]#, VDD_SRC, VSS_SRC

CPU IREF, CPU[1:0], CPU[1:0]#, VSS_CPU, VDD_CPU

PCI VDD_PCI, VSS_PCI, PCI[5:0], PCIF[2:0]

REF XTAL_OUT, XTAL_IN, VSS_REF, VDD_REF, REF

USB VDD_48, USB_48, VSS_48, DOT 96, DOT 96#

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

VDD_PCI

V SS_PCI

PCI_3

PCI_4

PCI_5

V SS_PCI

VDD_PCI

PCIF_ 0 /ITP_ EN

PCIF_ 1

PCIF_ 2

V DD_USB

UBS_48

V SS_USB

DOT_96

DOT_96#

FS_B/TEST_MODE

V TT_PWRGD#/PWRDW N

FS_A

SRC_1

SRC_1#

VDD_SRC

SRC_2

SRC_2#

SRC_3

SRC_3#

SRC_4/SA TA

SRC_4/SA TA #

VDD_SRC

PCI_2

PCI_1

PCI_0

FS_C/TEST_SEL

REF

VSS_REF

XTAL_IN

XTAL_OUT

VDD_REF

SDA

SCL

VSS_CPU

CPU_0

CPU_0#

VDD_CPU

CPU_1

IR EF

VSS_A

V DD_A

CPU_2_ITP/SRC_7

CPU_2_ITP/SRC_7#

V DD_SRC

SRC_6

SRC_6#

SRC_5

SRC_5#

VSS_SRC

CPU_1#

Signal

Signal

Signal

PCI

CPU

SRC

USB

Analog

REF

Loading...

Loading...