Intel

®

EP80579 Integrated Processor Product Line May 2010

Order Number: 320068-005US 63

High-Speed Design Concerns—Intel

®

EP80579 Integrated Processor Product Line

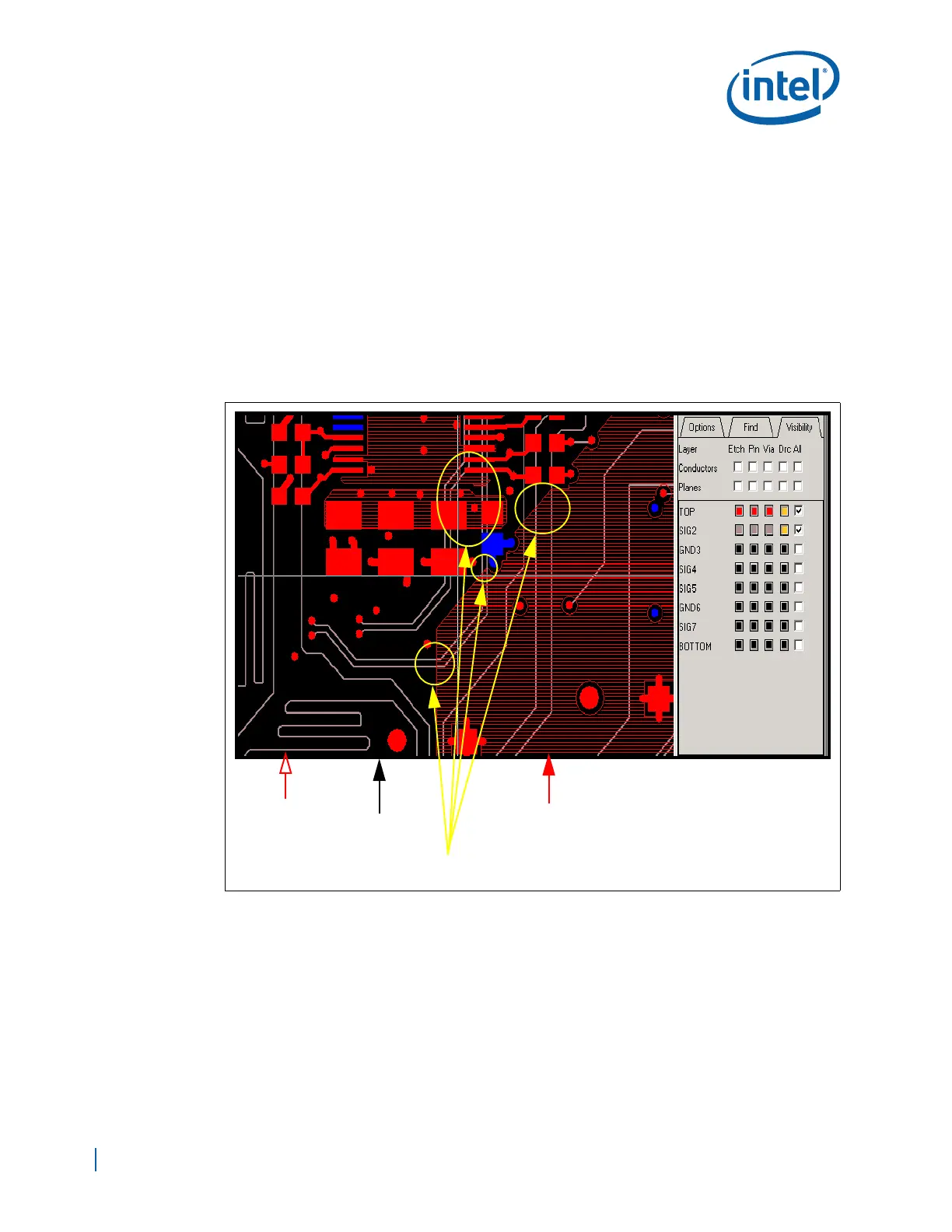

5.8.4 Signals Crossing Plane Splits

Signals that cross an adjacent layer’s plane boundary are undesirable for two reasons:

• The return current that runs in the reference plane wants to share its current with

the adjacent layer’s reference plane it just crossed over. The return current now

has to find a return path on the adjacent layer which will cause signal delay.

• The impedance of the trace will change each time it crosses a plane.

Figure 38 shows the improper method of signals crossing the adjacent layer’s plane

boundaries. Signal routing is done on layer 2, while layer 1 (striped area) contains

power and ground. Signals must be routed in a way to avoid this issue, such as routing

on a different layer or repositioning the signals to avoid the adjacent layer’s plane

boundary.

Figure 38. Signal Crossing Plane Splits

Layer 2

Layer 1

Signals crossing plane splits

Layer 2 Signals

Loading...

Loading...