Intel

®

EP80579 Integrated Processor Product Line May 2010

Order Number: 320068-005US 136

PCI Express* Interface—Intel

®

EP80579 Integrated Processor Product Line

For more information on PCI Express, see the PCI Express Base Specification, Rev. 1.1

and PCI Express Card Electromechanical Specification, Rev. 1.0 or later.

The EP80579 provides support for x8 port or x4 port. The x8 port can be divided into

two x4 ports or two x1 ports.

For the list of PCI Express signals, see the Intel

®

EP80579 Integrated Processor

Product Line Datasheet.

10.1 PCI Express Layout Design Guidelines

This section contains information and details for layout and routing guidelines.

One of the key points for PCI Express board design is to follow a set of rules to

minimize losses, jitter, crosstalk, and mode conversion for differential traces.

Loss is the differential voltage signal swing attenuation of the trace from transmitter to

receiver. The trace is subject to resistive, dielectric, and skin effect losses. Loss

increases as trace length or frequency increases. In addition, conductor loss increases

as trace width decreases. Vias and connectors that are a part of the interconnect also

introduce losses. Total loss allowed on the interconnect is 13.2 dB at 1.25 GHz.

Jitter, including jitter from crosstalk, consists of random and deterministic contributions

to signal edge timing that reduce the signal valid time. The total jitter on the

interconnect allowable is 120 ps.

Crosstalk is the coupling of energy from one signal trace to the other which results in

the signal voltage and phase change. There are two kinds of crosstalk, Far-End (FEXT)

and Near-End (NEXT). Whether the transmitter and receiver pairs are interleaved, the

Far-End can appear at the transmitter or receiver. Crosstalk within the differential pair

is not a concern. Crosstalk between differential pairs can be minimized by keeping a

large pair-to-pair spacing compared to spacing within a pair. Stripline traces show far

less Far-End crosstalk (FEXT) than microstrip.

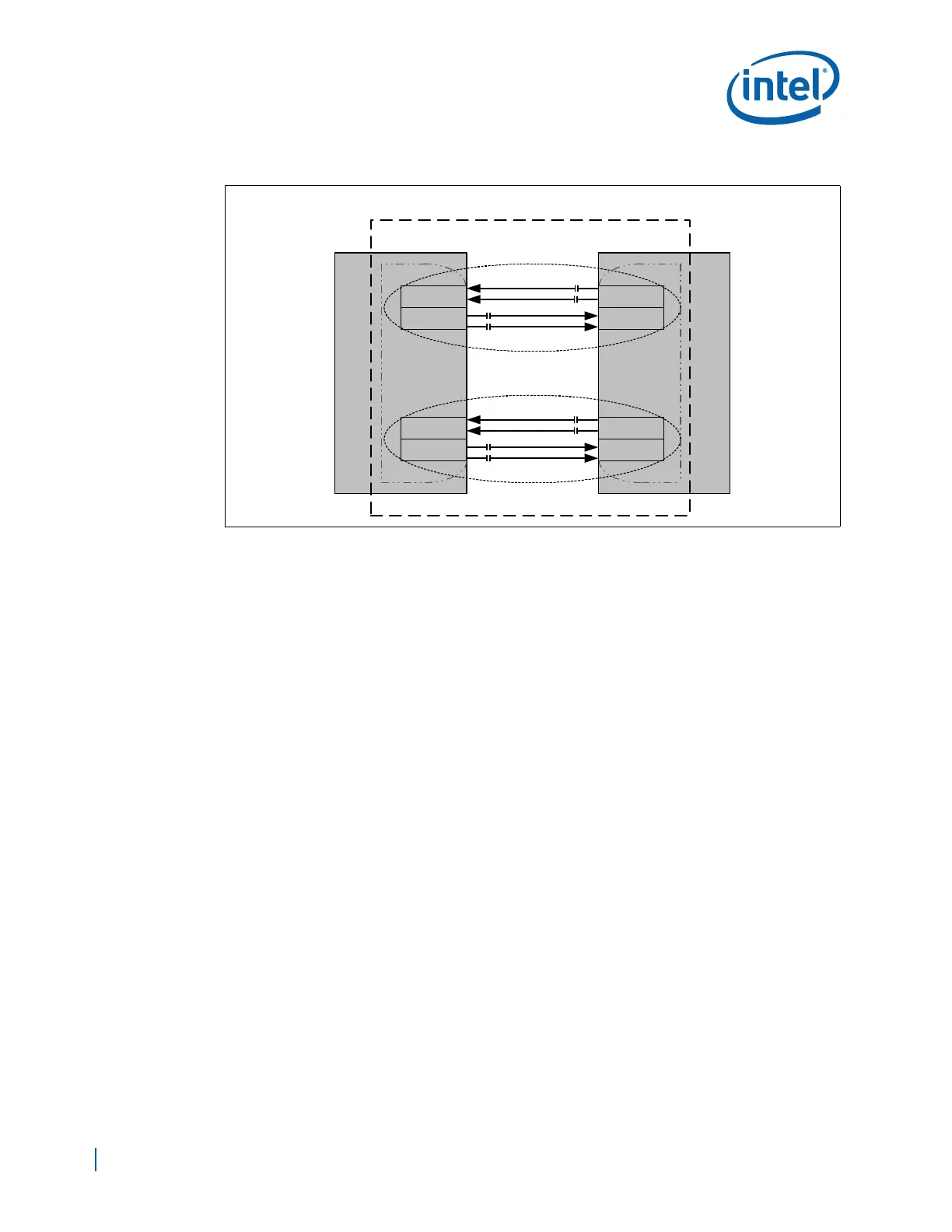

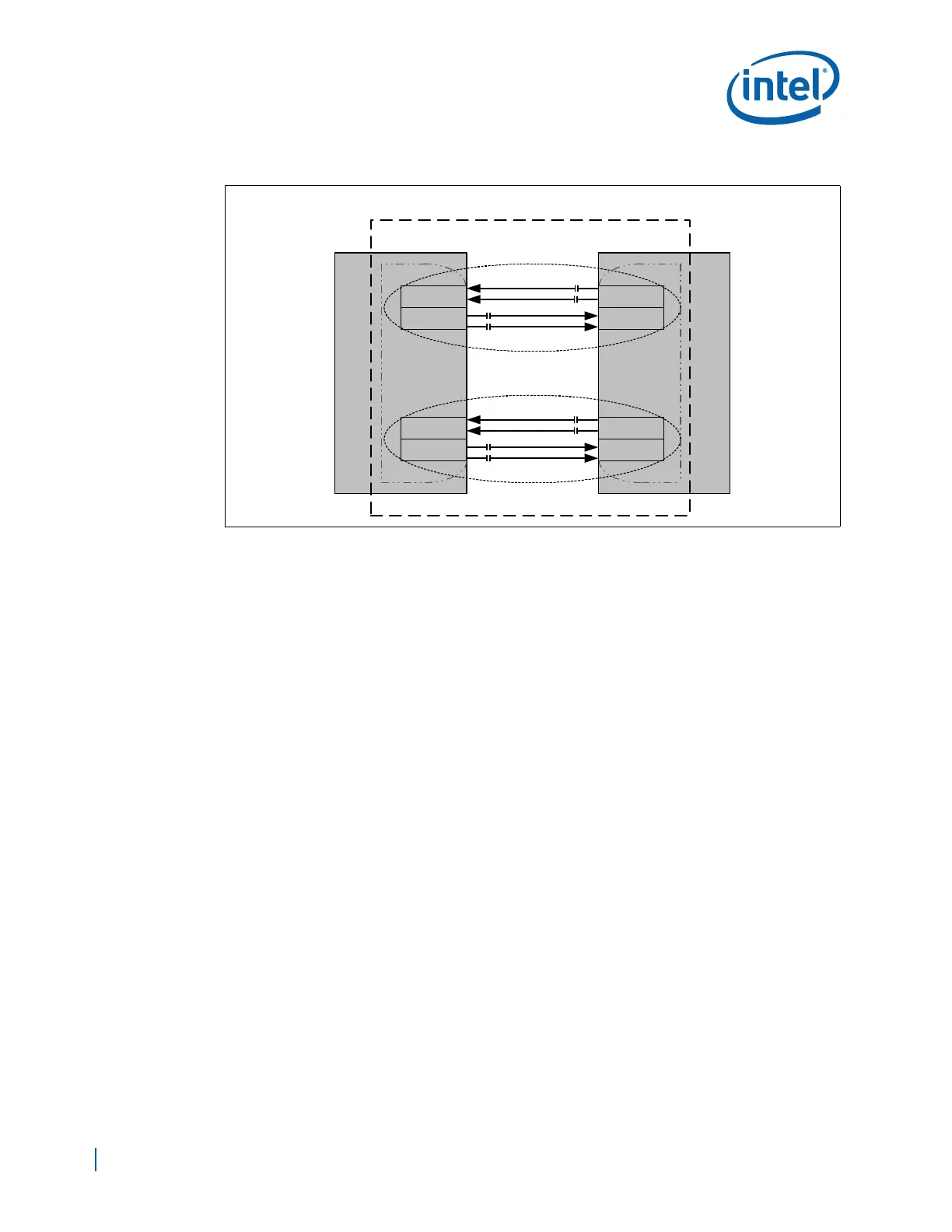

Figure 86. PCI Express* Interconnect

Rx

Tx

Device

Tx

Rx

Rx

Device

Rx

Tx

LANE 0

LANE 1

LINK (x2)

P

O

R

T

P

O

R

T

Tx

AC coupling capacitors

AC coupling capacitors

Loading...

Loading...