Intel

®

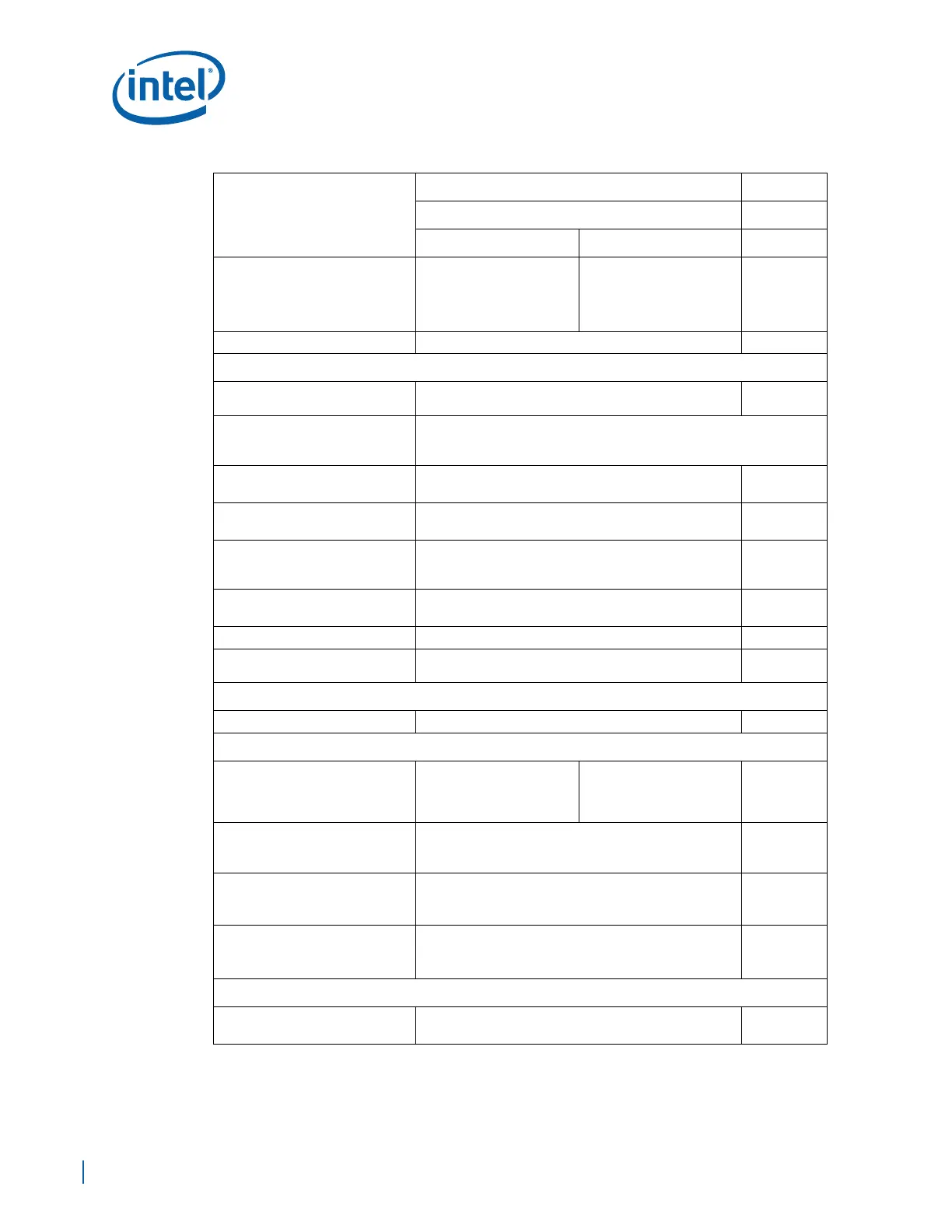

EP80579 Integrated Processor Product Line—System Memory Interface (Memory Down)

Intel

®

EP80579 Integrated Processor Product Line

Platform Design Guide May 2010

343 Order Number: 320068-005US

Trace-to-Trace spacing (e2e) 15 mils (min)

• Inter-pair Spacing:--

DQS/DQS# = 6 mils

(min)

• Pair-to-Pair Spacing:

15 mils (min)

Clearance from other signals 20.0 mils (min)

Board Routing Guidelines

Total Trace Length (TTL) = (Lp +

L0 + L1 + L2 + L3)

Total Trace Length = 2.0 in - 6.0 in

Lp

Package Length:

• See the Intel

®

EP80579 Integrated Processor Product Line

Datasheet for package length information.

L0

Microstrip Break-out:

• Trace Length = 0.5 in (max)

L1

Board Route (Microstrip or Stripline)

• Trace Length = 1.5 in (min) - 4.0 in (max)

L2

Microstrip Board Route:

• Trace Length = 0.3 in(max) if L1 is Stripline routed

on L3/L5/L6/L8

L3

Microstrip Break-in

• Trace Length = 0.5 in (max)

Break-out/Break-in Trace Width 4.0 mils

Break-out/Break-in Trace-to-Trace

Spacing

4.0 mils

Series Termination

Series Resistor (Rsd) 22Ω ±1%

Routing Length Matching Rules

DQS-to-DQS# Inter-pair Length

Matching

• Match total length of

DQS to DQS# to within

±10 mils

• DQS = DQS# ±10 mils

DQ/DM Data Byte Lane Length

Matching

Match total Length of data byte lane signals (DQ/DM) to

within 20 mils

• Max(DQ/DM) - Min(DQ/DM) </= 20 mils

DQS-to-DQ/DM Length Matching

Match total length of DQ/DM to DQS to within ±20 mils

• DQ/DM minimum Length = DQS - 20 mils

• DQ/DM maximum Length = DQS + 20 mils

DQS-to-Clock Length Matching

Match total length of DQS to clocks to within ±500 mils

• DQS/DQS# minimum Length = Clock - 500 mils

• DQS/DQS# maximum Length = Clock + 500 mils

ODT Settings

Enable ODT

• Controller ODT = 120Ω

• SDRAM ODT = 150Ω

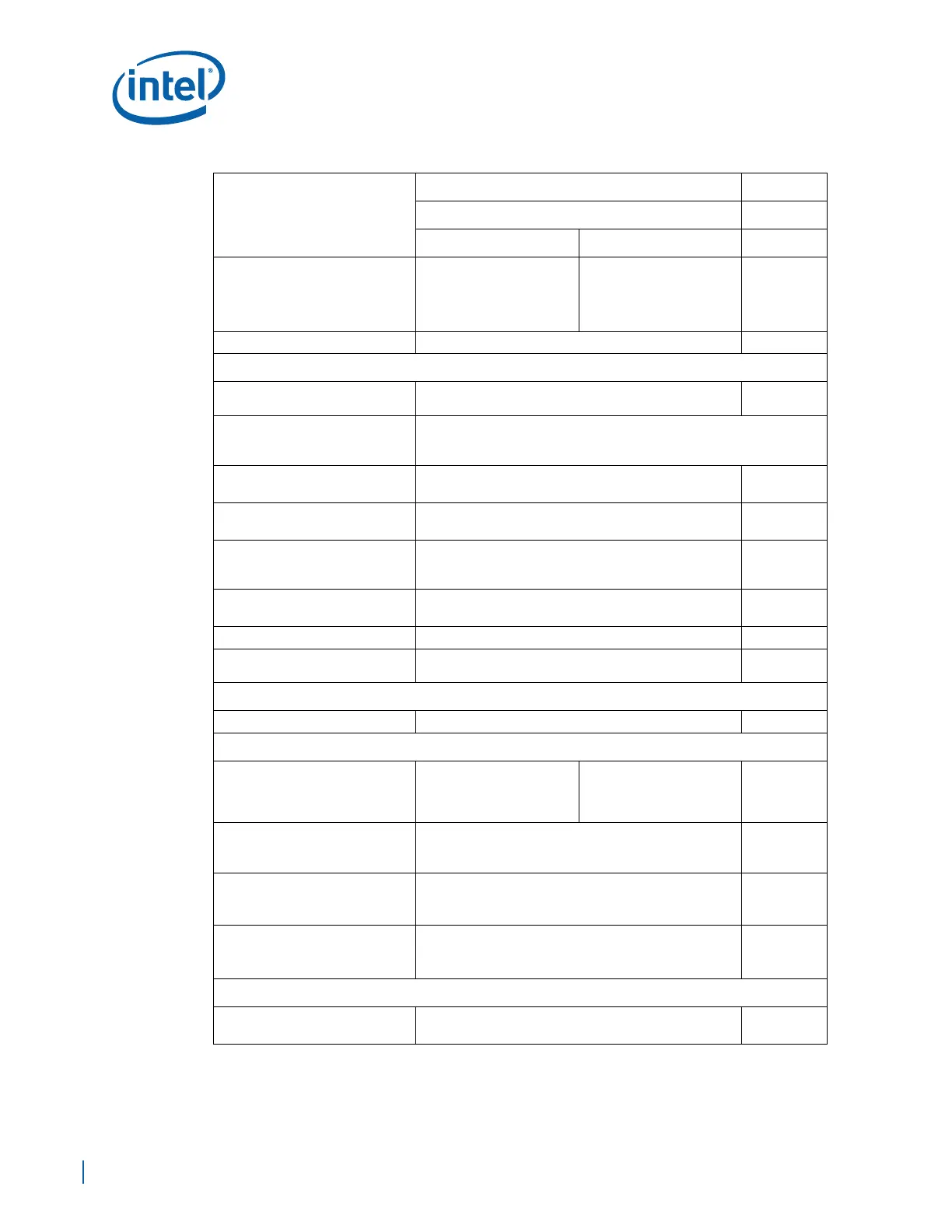

Table B-29. Data and Strobe Signal Group Routing Guidelines (Sheet 2 of 2)

Parameter

Routing Guidelines Figure

Data Byte Lane

Data & Data Mask Strobe

Loading...

Loading...