Intel

®

EP80579 Integrated Processor Product Line May 2010

Order Number: 320068-005US 23

Introduction—Intel

®

EP80579 Integrated Processor Product Line

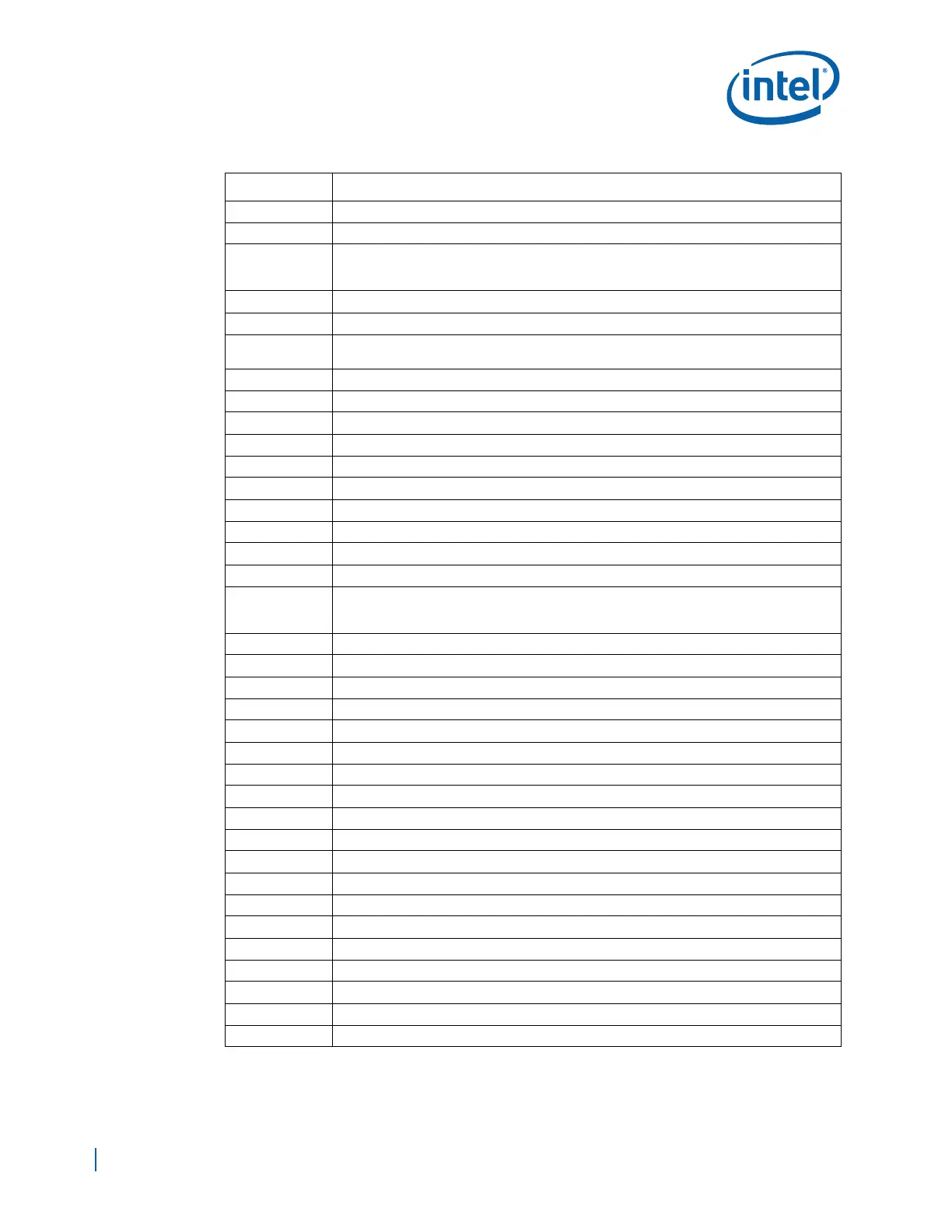

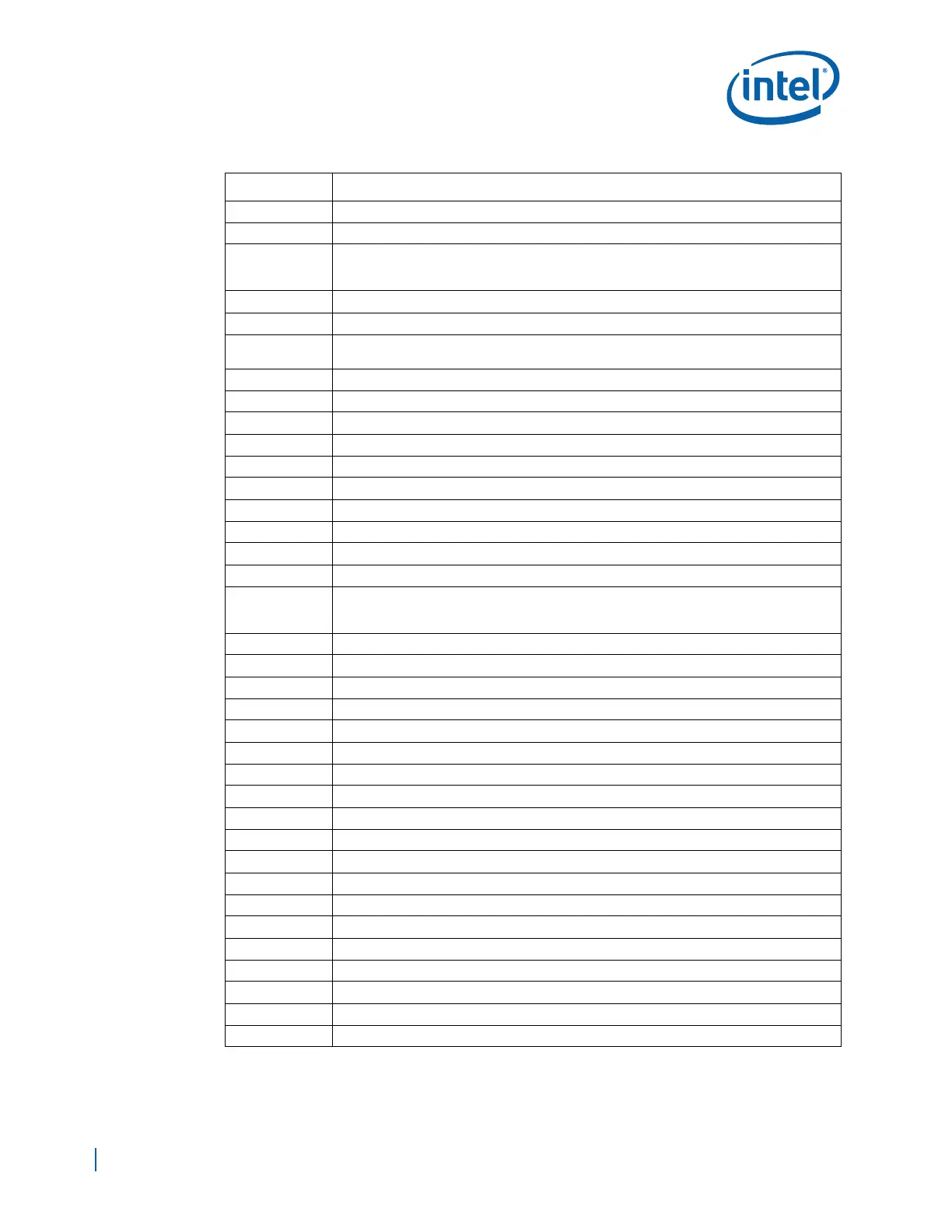

OS Operating System

P2P Peer-to-Peer

PCI

Peripheral Component Interconnect Local Bus, a 32- or 64-bit bus with multiplexed

address and data lines that is primarily intended for use as an interconnect mechanism

within a system between processor/memory and peripheral components or add-in cards.

PCM Pulse Code Modulation

PEC Packet Error Checking, this is an SMBus 2.0 feature

PIRQx

Legacy PCI interrupt architecture that encodes interrupts on one of eight side-band signals

(PIRQ[H:A]).

PLL Phase-Locked Loop

POC Power On Configuration

RDMA Remote Direct Memory Access

RFL Receive FIFO Level

RMW Read-Modify-Write operation

RTC Real-Time Clock

RTCRESET# Signal that resets the RTC well (but does not clear the RTC RAM memory contents).

SATA Serial Advanced Technology Attachment

SATA* Serial ATA, an industry specification of the interface for storage controllers and devices.

SEC Single-bit Error Correct

SEC/DED

Single Error Correct/Double Error Detect, a specific data protection algorithm that

distributes data and ECC across 144 bits. Enables correction of single bit errors. Allows

detection of double bit errors.

SM M-Unit attached to the System Memory (Convention taken from IA CHAP event definition)

SMBus System Management Bus

SMM System Management Mode

SPD Serial Presence Detect

STR Suspend To RAM

TAP Test Access Port used for testability and debug of the component

TCP Transmission Control Protocol

TDM Time Division Multiplexed

TDR Time Domain Reflectometry

TFL Transit FIFO Level

USB Universal Serial Bus

VCC Used to signal circuit logic voltage

VCXO Voltage Controlled Crystal Oscillator

VDD Used to signify DIMM logic supply voltage

VREF Voltage Reference

VSS Used to signify ground connection

VTT Used to signify signal termination voltage

WDT Watch Dog Timer

XDP eXtended Debug Port

Table 2. Acronyms and Terminology (Sheet 3 of 3)

Acronym Definition

Loading...

Loading...