Intel

®

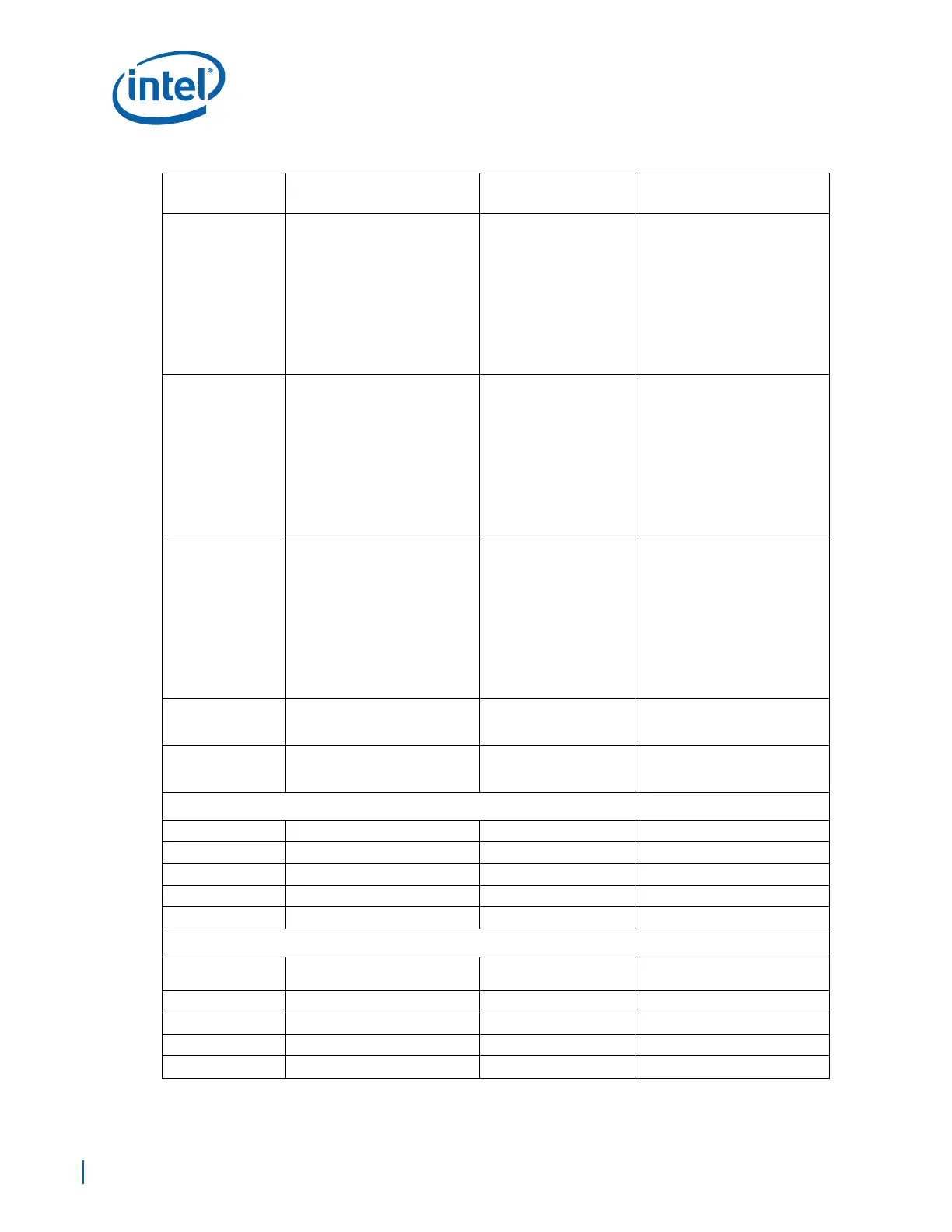

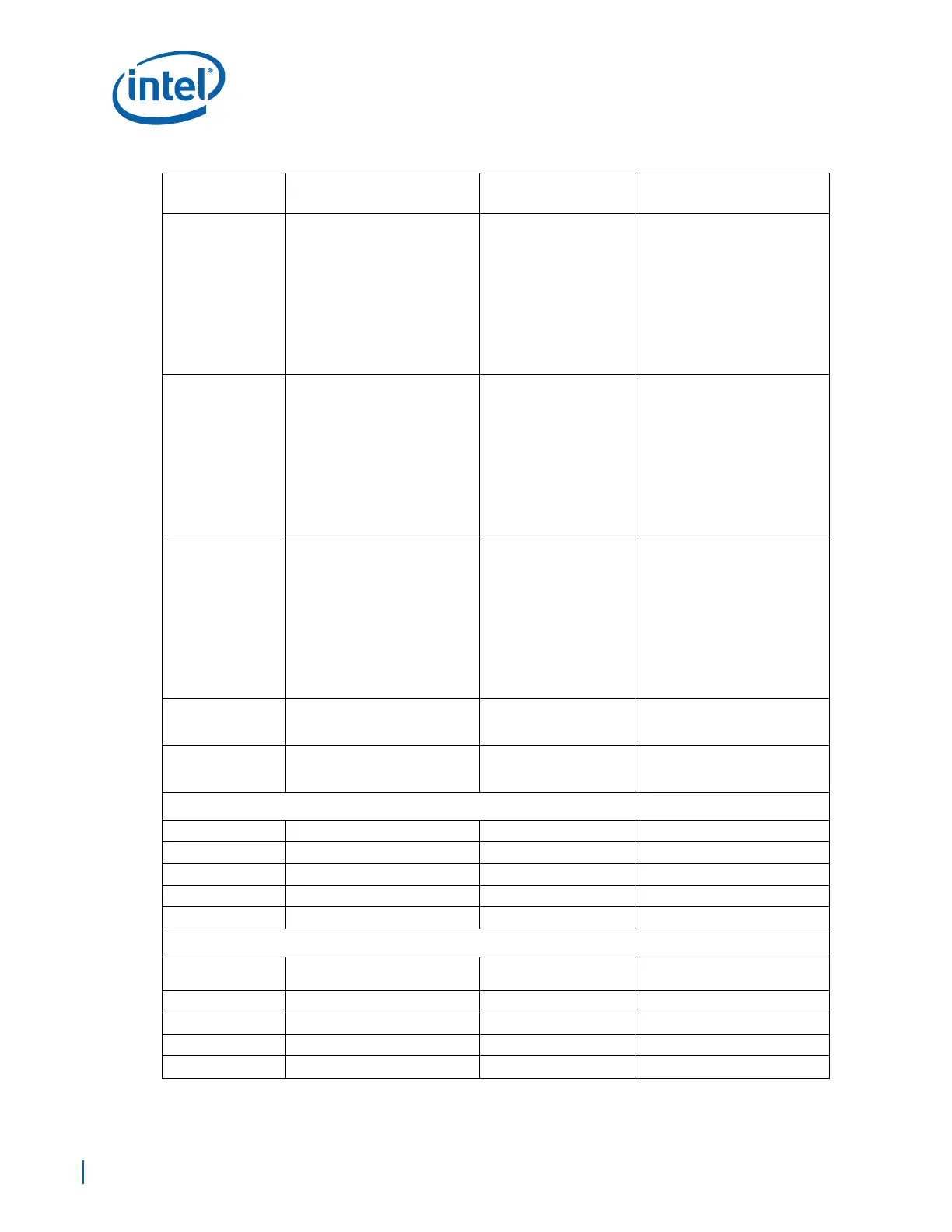

EP80579 Integrated Processor Product Line—Layout Checklist

Intel

®

EP80579 Integrated Processor Product Line

Platform Design Guide May 2010

280 Order Number: 320068-005US

EX_DATA[15:0]

Zo = 50

Ω +/- 10%

Trace Width:

Brakeout Trace Width 4 mils

Microstrip: 5.5 mils

Stripline: 4.5 mils (L3/L8)

Airgap Spacing:

Brakeout spacing Min=4mils

Microstrip: 12 mils

Stripline: 10 mils

Breakout: Max = 1 in.

Breakin: Max = 1 in.

Length:

LDC_Total = LCS_Total

+/-500mils, Not to

exceed 16 inch at 33 MHz

See Section 22.3.4, “Data and

Control Star Topology”.

EX_RD#

EX_WR#

EX_BE[1:0]#

EX_RDY[3:0]#

EX_PARITY[1:0]

Zo = 50

Ω +/- 10%

Trace Width:

Brakeout Trace Width 4 mils

Microstrip: 5.5 mils

Stripline: 4.5 mils (L3/L8)

Airgap Spacing:

Brakeout spacing Min=4mils

Microstrip: 12 mils

Stripline: 10 mils

Breakout: Max = 1 in.

Breakin: Max = 1 in.

Length:

LDC_Total = LCS_Total

+/-500mils, Not to

exceed 16 inch at 33 MHz

See Section 22.3.4, “Data and

Control Star Topology”.

EX_ALE

EX_BURST

EX_IOWAIT#

Zo = 50

Ω +/- 10%

Trace Width:

Brakeout Trace Width 4 mils

Microstrip: 5.5 mils

Stripline: 4.5 mils (L3/L8)

Airgap Spacing:

Brakeout spacing Min=4mils

Microstrip: 12 mils

Stripline: 10 mils

Breakout: Max = 1 in.

Breakin: Max = 1 in.

Length:

Not to exceed 16 inch at

33 MHz

See Section 22.3.4, “Data and

Control Star Topology”.

EX_RCOMPP Zo = 50

Ω +/- 10%

Routing Length LT:

Max = 0.5 in.

Place the RCOMPP

(compensation resistor) as close

as possible to EP80579

.

EX_RCOMPN Zo = 50 Ω +/- 10%

Routing Length LT:

Max = 0.5 in.

Place the RCOMPN

(compensation resistor) as close

as possible to EP80579

.

Synchronous Serial Port (SSP) Interface

SSP_SCLK Zo = 50

Ω +/- 10%

SSP_SFRM Zo = 50

Ω +/- 10%

SSP_TXD Zo = 50 Ω +/- 10%

SSP_RXD Zo = 50

Ω +/- 10%

SSP_EXTCLK Zo = 50

Ω +/- 10%

IEEE 1588 Hardware-Assist Interface

TS_TESTMODE_DAT

A

Zo = 50

Ω +/- 10%

TS_PPS Zo = 50

Ω +/- 10%

ASMSSIG Zo = 50 Ω +/- 10%

AMMSSIG Zo = 50

Ω +/- 10%

TSYNC_RX_SNAP Zo = 50

Ω +/- 10%

Table 97. Layout Checklist (Sheet 12 of 13)

Signal Name

Trace Geometry and

Impedance

Length Requirements Comments

Loading...

Loading...