Intel

®

EP80579 Integrated Processor Product Line May 2010

Order Number: 320068-005US 279

Layout Checklist—Intel

®

EP80579 Integrated Processor Product Line

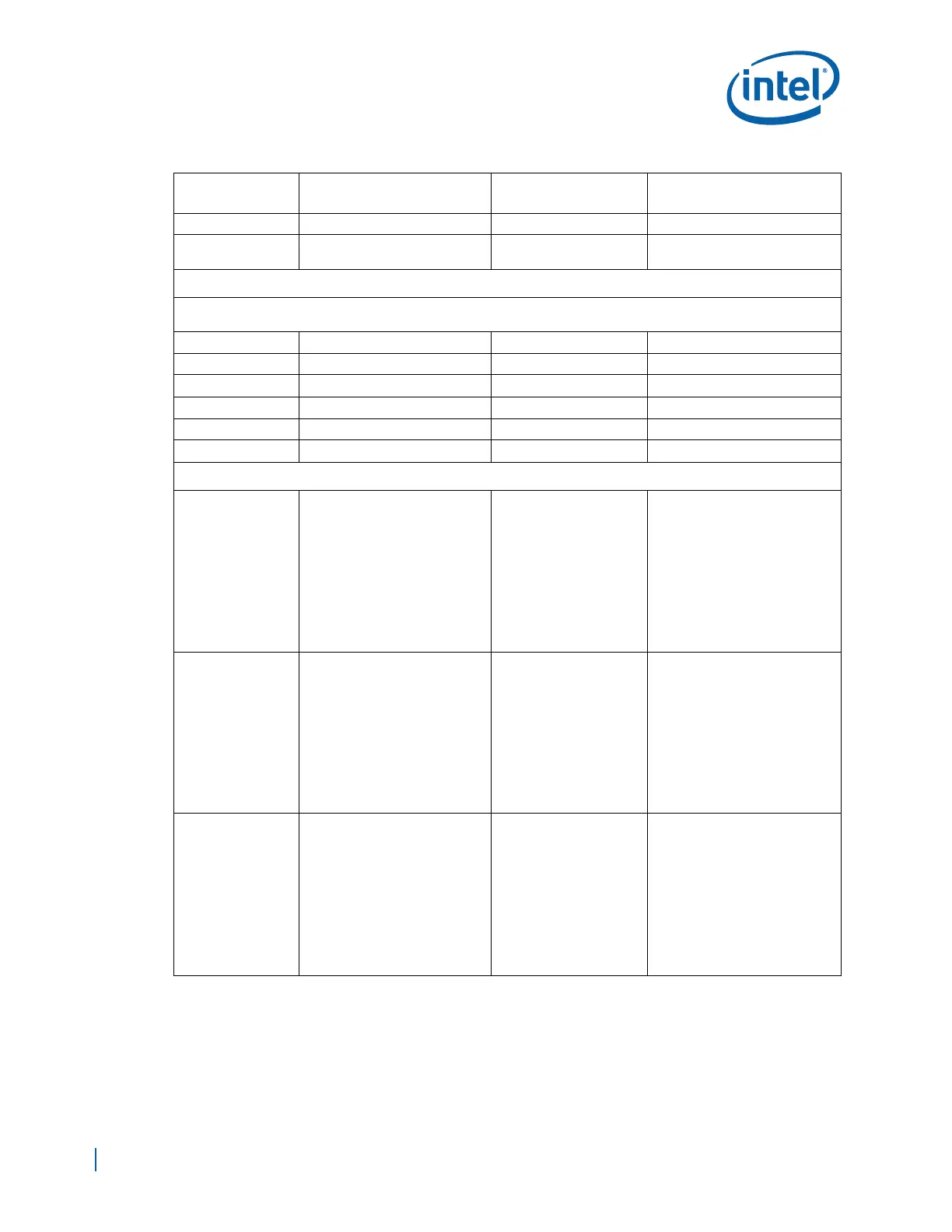

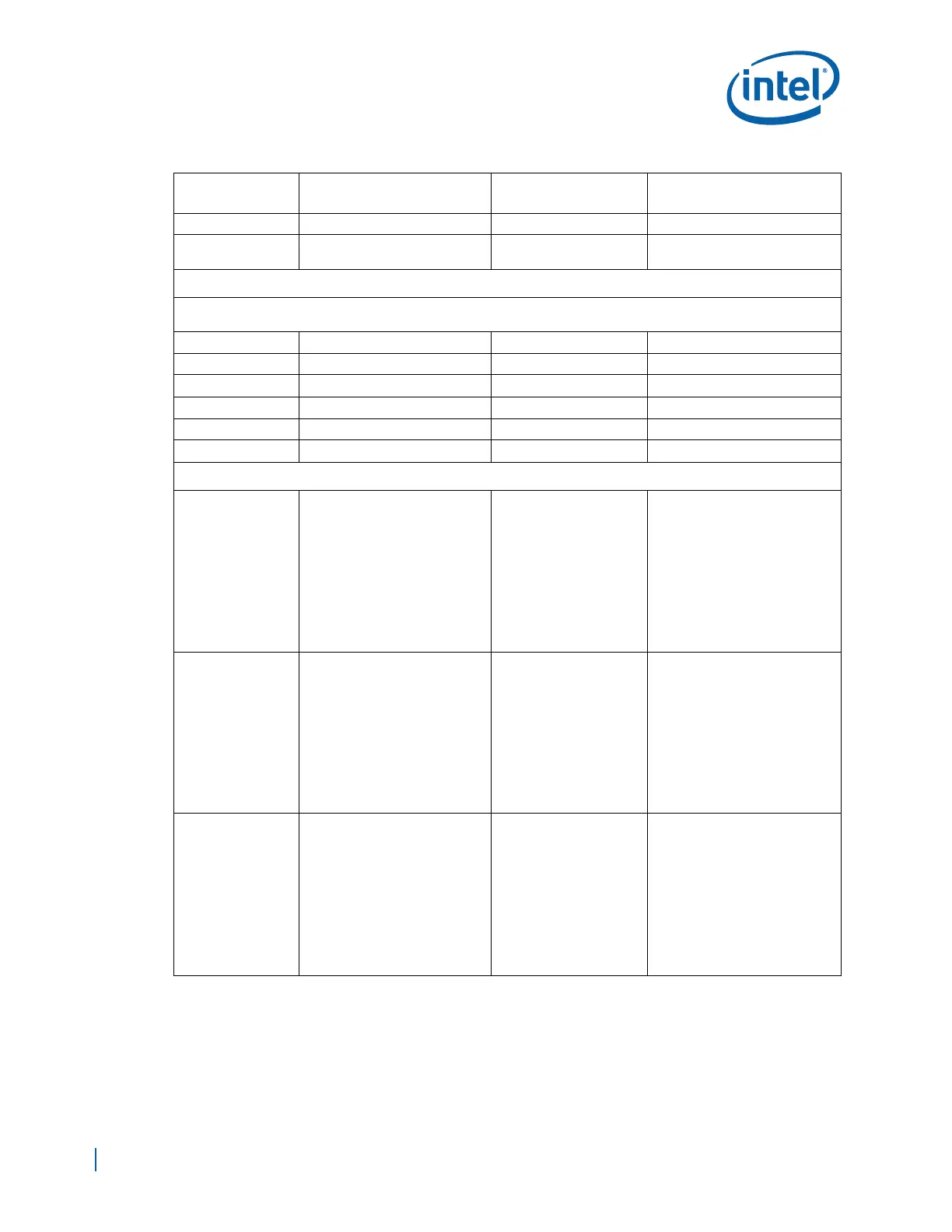

SYS_PWR_OK Zo = 50

Ω +/- 10%

GBE_AUX_PWR_GO

OD

Zo = 50

Ω +/- 10%

Time Division Multiplexing (TDM) Interface

Note: Certain EP80579 SKUs may not contain this feature. Feature must be enabled with EP80579 Software. See

EP80579 “SKU Features” in the EP80579 Software Documentation for detailed Information

Rx_CLK[2:0] Zo = 50

Ω +/- 10%

Tx_CLK[2:0] Zo = 50

Ω +/- 10%

Tx_FRAME[2:0] Zo = 50

Ω +/- 10%

Tx_DATA_OUT[2:0] Zo = 50

Ω +/- 10%

Rx_FRAME[2:0] Zo = 50

Ω +/- 10%

Rx_DATA_IN[2:0] Zo = 50

Ω +/- 10%

Local Expansion Bus (LEB) Interface

EX_ADDR[24:0]

Zo = 50

Ω +/- 10%

Trace Width:

Brakeout Trace Width 4 mils

Microstrip: 5.5 mils

Stripline: 4.5 mils (L3/L8)

Airgap Spacing:

Brakeout spacing Min=4mils

Microstrip: 12 mils

Stripline: 10 mils

Breakout: Max = 1 in.

Breakin: Max = 1 in.

Length:

LADDR_Total = LCS_Total

+/-500mils, Not to

exceed 16 inch at 33 MHz

See Section 22.3.3, “Address

Star Topologies”.

EX_CLK

Zo = 55

Ω +/- 10%

Trace Width:

Brakeout Trace Width 4 mils

Microstrip: 5.5 mils

Stripline: 4.5 mils (L3/L8)

Airgap Spacing:

Brakeout spacing Min=4mils

Microstrip: 12 mils

Stripline: 10 mils

Breakout: Max = 1 in.

Breakin: Max = 1 in.

See Section 8.2.3, “CLK33

Group”.

EX_CS[7:0]#

Zo = 50

Ω +/- 10%

Trace Width:

Brakeout Trace Width 4 mils

Microstrip: 5.5 mils

Stripline: 4.5 mils (L3/L8)

Airgap Spacing:

Brakeout spacing Min=4mils

Microstrip: 12 mils

Stripline: 10 mils

Breakout: Max = 1 in.

Breakin: Max = 1 in.

Length:

LCS_Total = 16 in. (Max)

See Section 22.3.2, “Chip Select

Topologies”.

Table 97. Layout Checklist (Sheet 11 of 13)

Signal Name

Trace Geometry and

Impedance

Length Requirements Comments

Loading...

Loading...