Intel

®

EP80579 Integrated Processor Product Line May 2010

Order Number: 320068-005US 304

Schematics Checklist—Intel

®

EP80579 Integrated Processor Product Line

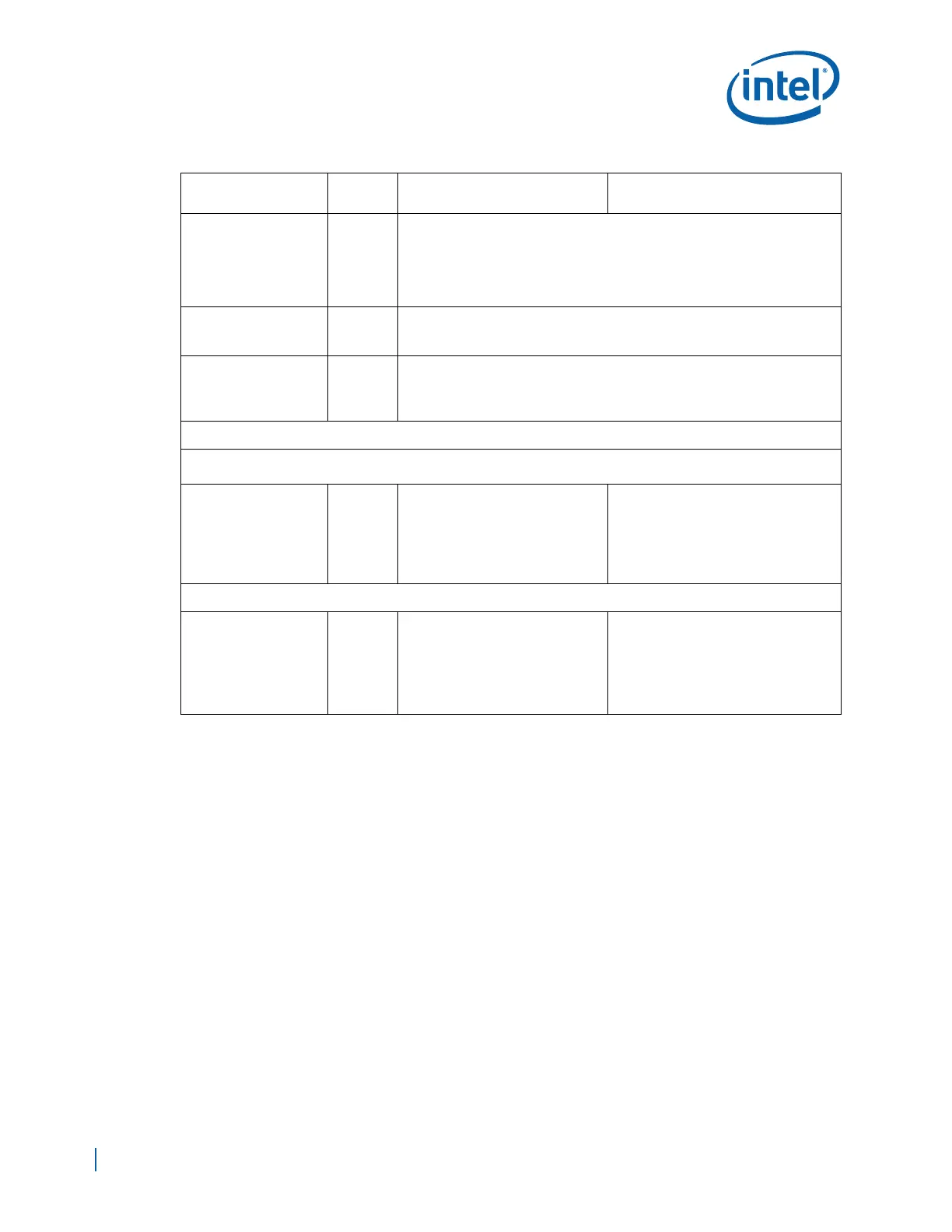

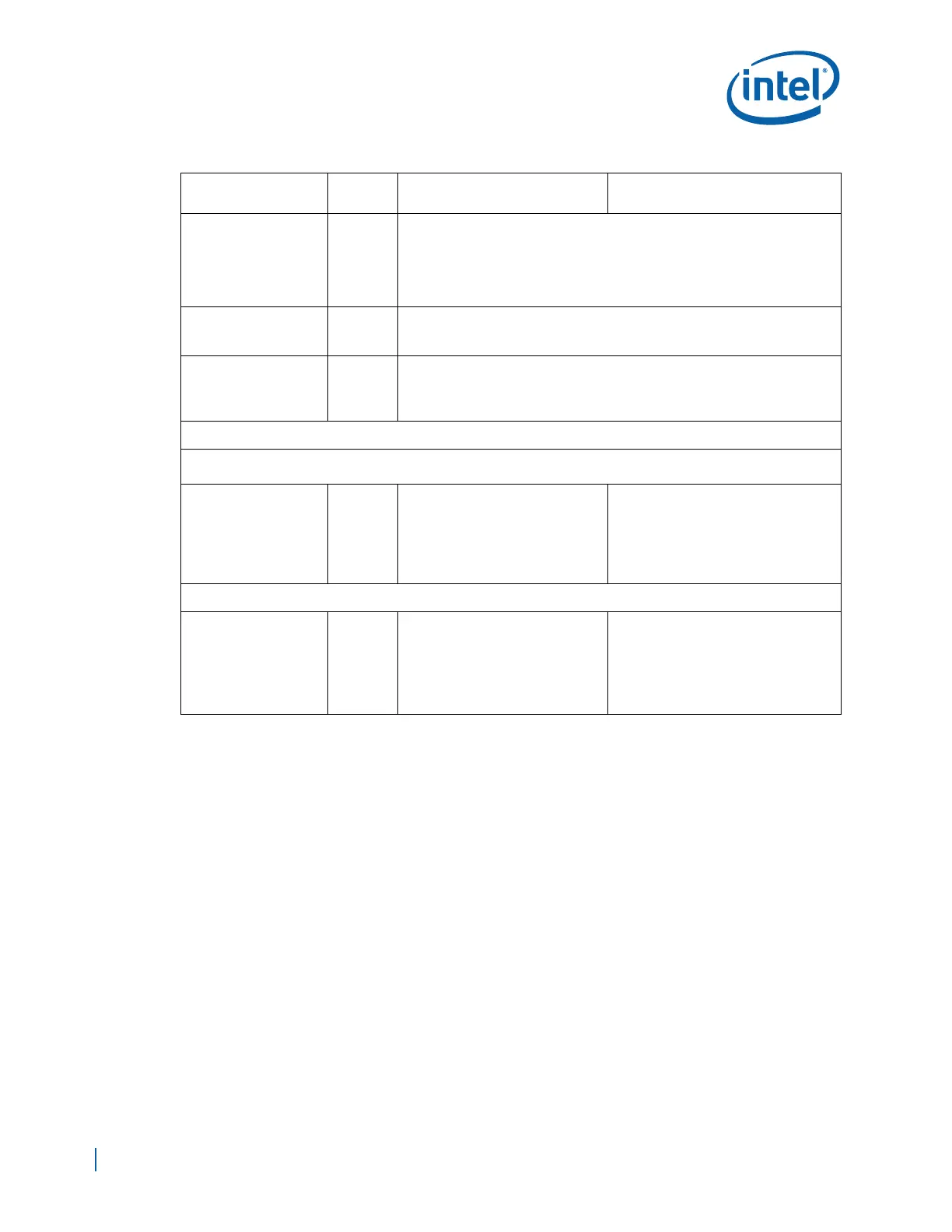

EESK O

• Connect to EEPROM Shift Clock input (SK)

• Connect through a 4.7KΩ ±5% resistor to Ground.

Note:

• Can be left as NC when none of GBE ports is connected to an interfacing

device

GBE_PME_WAKE OD O

• Connect to EP80579 PME# Input

• Pull-up to EP80579 3.3V Standby (VCCPSUS) supply through a 10 KΩ ±5%

resistor

GBE_AUX_PWR_GOOD I

• Connect to Platform GBE_AUX_PWR_GOOD

Note:

• Connect to SYS_PWR_OK if standby voltages are not generated.

3-Port Time Division Multiplexing (TDM) Interface

Note: Certain EP80579 SKUs may not contain this feature. Feature must be enabled with EP80579 software. See

EP80579 “SKU Features” in the EP80579 Software Documentation for detailed information.

Rx_CLK[2:0],

Rx_FRAME[2:0],

Rx_DATA_IN[2:0],

Tx_CLK[2:0],

Tx_FRAME[2:0],

Tx_DATA_OUT[2:0]

I/O

• Connect appropriately to the

three mezzanine card

connectors.

• Each connector supports two

TDM (HSS) ports to be

compatible with previous voice

mezzanine cards.

Note:

• If an interface is not used or

connected to a device, each

interface signal should be pulled

high through 10 KΩ resistors.

Local Expansion Bus (LEB) Interface (See Section 22.3.3 for more details)

EX_ALE O

• Address Latch Enable

• Used for multiplexed address/

data bus accesses

• Used in Intel, Motorola, and HSS

multiplexed modes of operation

Note:

• Can be left as no connect (NC)

when the interface is not connected

to an interfacing device or not used

Table 100. Schematic Checklist (Sheet 21 of 26)

Checklist Items

I/O Type

(Default)

Recommendations Comments

Loading...

Loading...