PowerPC e500 Core Family Reference Manual, Rev. 1

2-28 Freescale Semiconductor

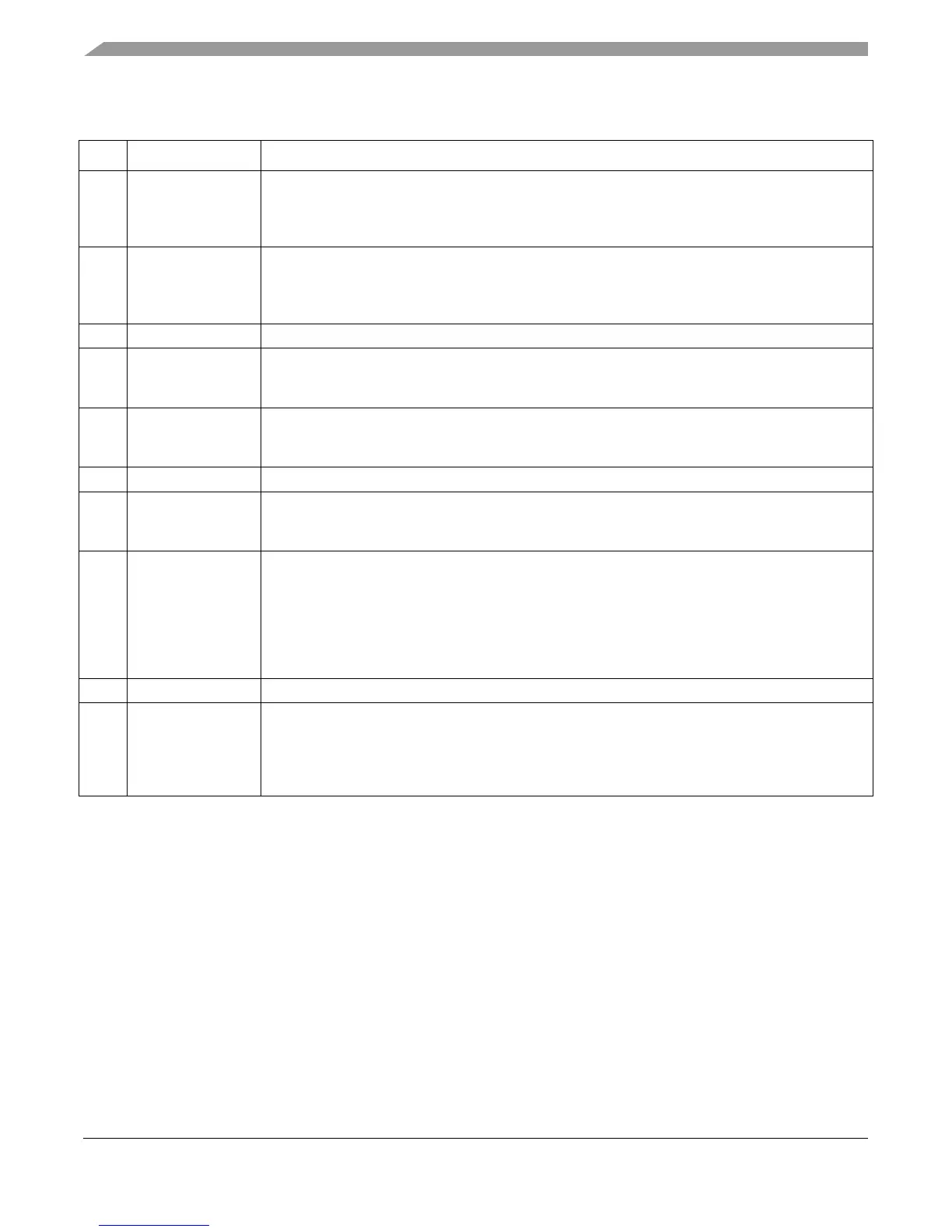

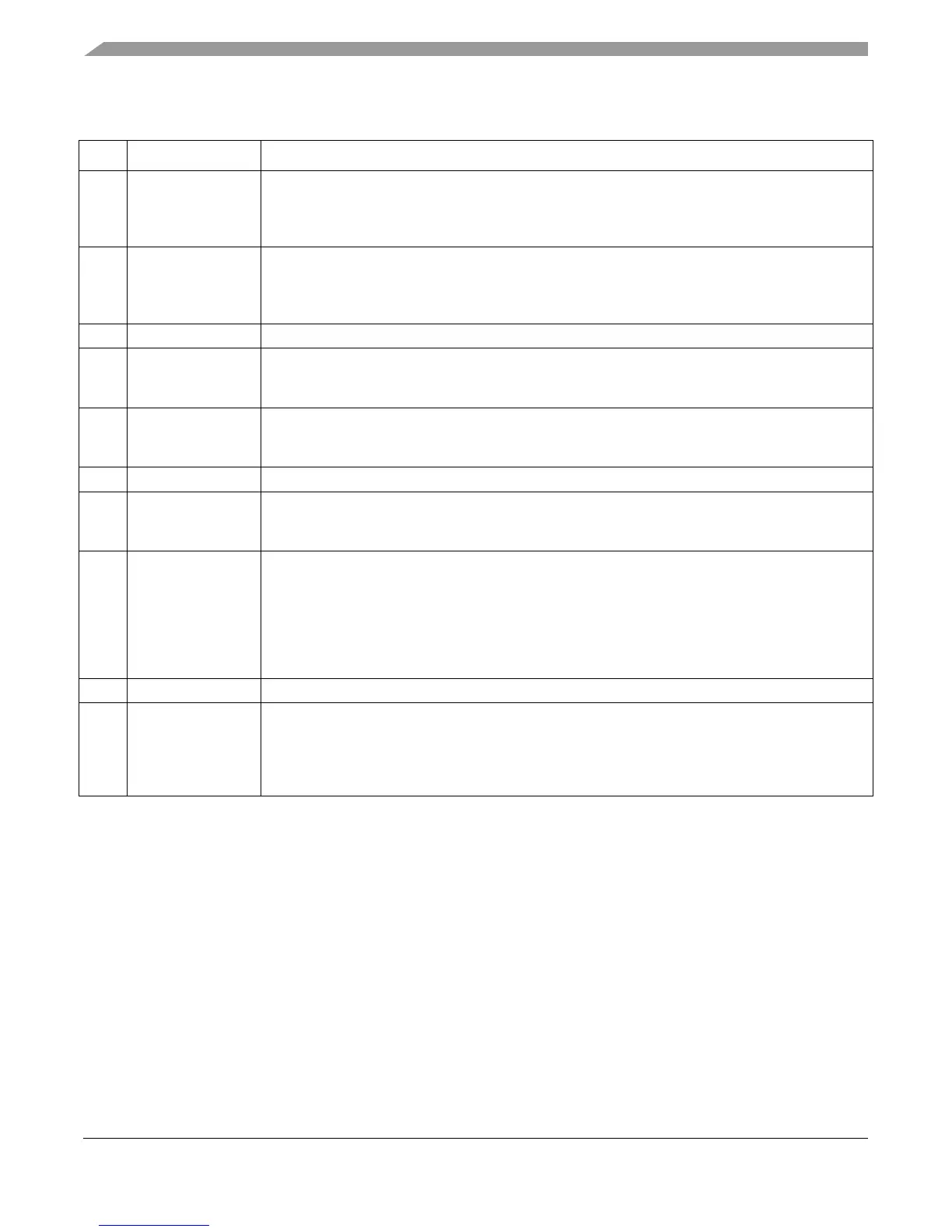

Register Model

41 NAP Nap power management mode. If MSR[WE] is set, this bit controls the

nap

output signal.

Interpretation of this bit is handled by integrated system logic.

0

nap

is not asserted.

1

nap

is asserted.

42 SLEEP Configure for sleep power management mode. If MSR[WE] is set, this bit controls the

sleep

output

signal. Interpretation of this bit is handled by integrated system logic.

0

sleep

is not asserted

1

sleep

is asserted

43–48 — Reserved, should be cleared.

49 TBEN Time base and decrementer enable

0 Time base disabled

1 Time base enabled

50 SEL_TBCLK Select time base clock

0 Time base is based on the processor clock

1 Time base is based on TBCLK input

51–55 — Reserved, should be cleared.

56 EN_MAS7_UPDATE Enable MAS7 update (e500v2 only). Enables updating MAS7 by tlbre and tlbsx.

0 MAS7 is not updated by a tlbre or tlbsx.

1 MAS7 is updated by a tlbre or tlbsx.

57 DCFA Data cache flush assist (e500v2 only). Force data cache to ignore invalid sets on miss replacement

selection.

0 The data cache flush assist facility is disabled

1 The miss replacement algorithm ignores invalid entries and follows the replacement sequence

defined by the PLRU bits. This reduces the series of uniquely addressed load or dcbz instructions

to eight per set. The bit should be set just before beginning a cache flush routine and should be

cleared when the series of instructions is complete.

58–62 — Reserved, should be cleared.

63 NOPTI No-op the data and instruction cache touch instructions.

0 dcbt, dcbtst, and icbt are enabled, as defined by the EIS. Note that on the e500, if CT = 0, icbt

is always a no-op, regardless of the value of NOPTI. If CT = 1, icbt does a touch load to the L2

cache.

1 dcbt, dcbtst, and icbt are treated as no-ops; dcblc and dcbtls are not treated as no-ops.

Table 2-14. HID0 Field Descriptions (continued)

Bits Name Description

Loading...

Loading...