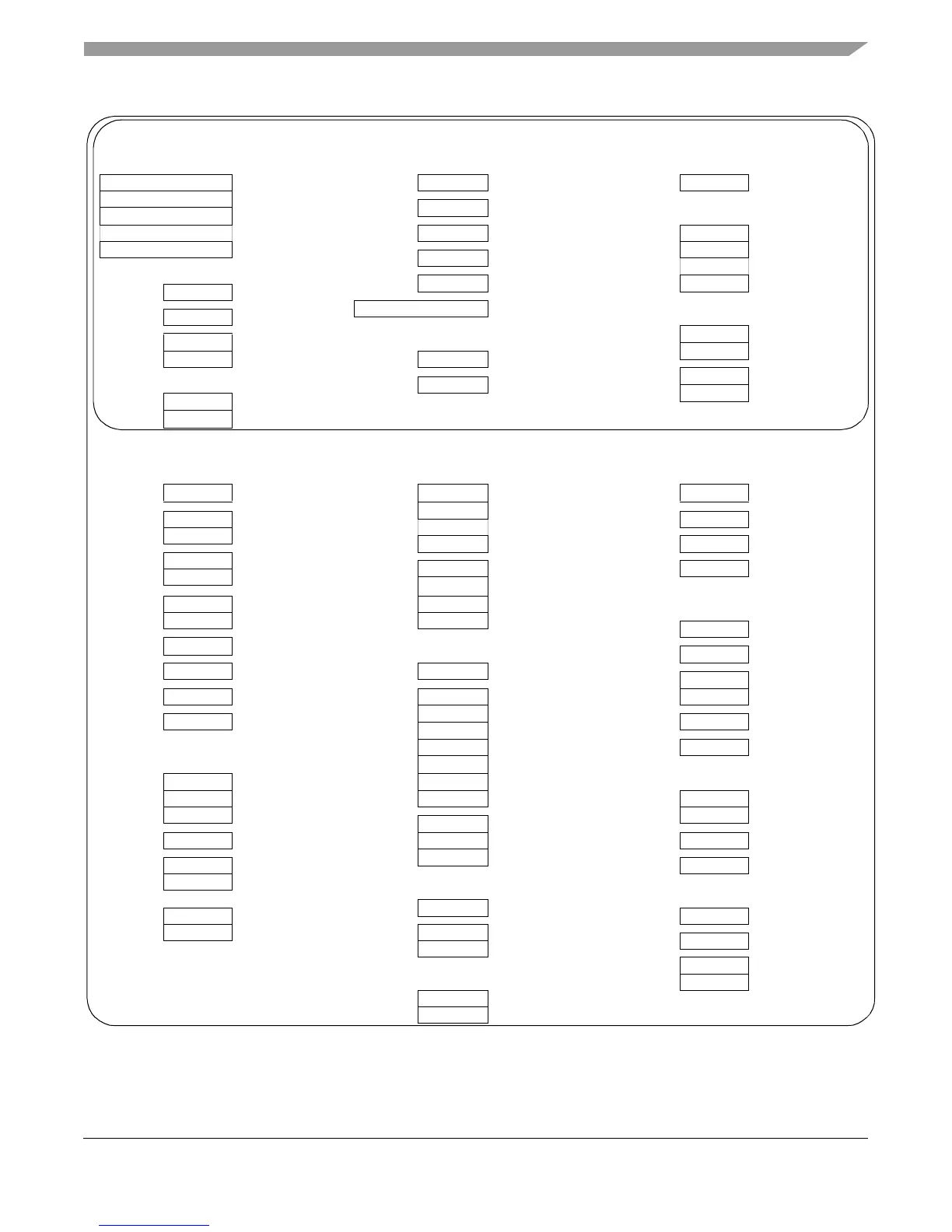

Register Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 2-3

Figure 2-1. e500 Register Model

User-Level Registers

General-Purpose Registers Instruction-Accessible Registers User General SPR (Read/Write)

0 31 32 63 0 31 32 63 32 63

User SPR

general 0

(upper) GPR0 (lower)

General-

purpose

registers

CR Condition register

spr 256 USPRG0

GPR1

spr 9

CTR

Count register

General SPRs (Read-Only)

GPR2

spr 8 LR Link register spr 259 SPRG3

SPR general

registers 3–7

GPR31 spr 260 SPRG4

spr 1 XER Integer exception

register

• • •

Performance Monitor PMRs (Read-Only)

spr 512 SPEFSCR

1

SPE FP status/control

register

spr 263 SPRG7

pmr 384

UPMGC0

1

1

These registers are defined by the EIS

Global control register

ACC

1

Accumulator

Time-Base Registers (Read-Only)

pmr 0–3

UPMCs

1

Counter

registers 0–3

Miscellaneous Registers

spr 268

TBL

Time base

lower/upper

pmr 128–131

UPMLCas

1

Local control registers

a0–a3, b0–b3

spr 269

TBU

pmr 256–259 UPMLCbs

1

spr 513

BBEAR

3

Branch buffer entry

address register

spr 526

AT BL

1, 2

Alternate time base

lower/upper

L1 Cache (Read-Only)

spr 514

BBTAR

3

Branch buffer target

address register

spr 527

AT BU

1, 2

spr 515

L1CFG0

1

L1 cache

configuration registers

0–1spr 516

L1CFG1

1

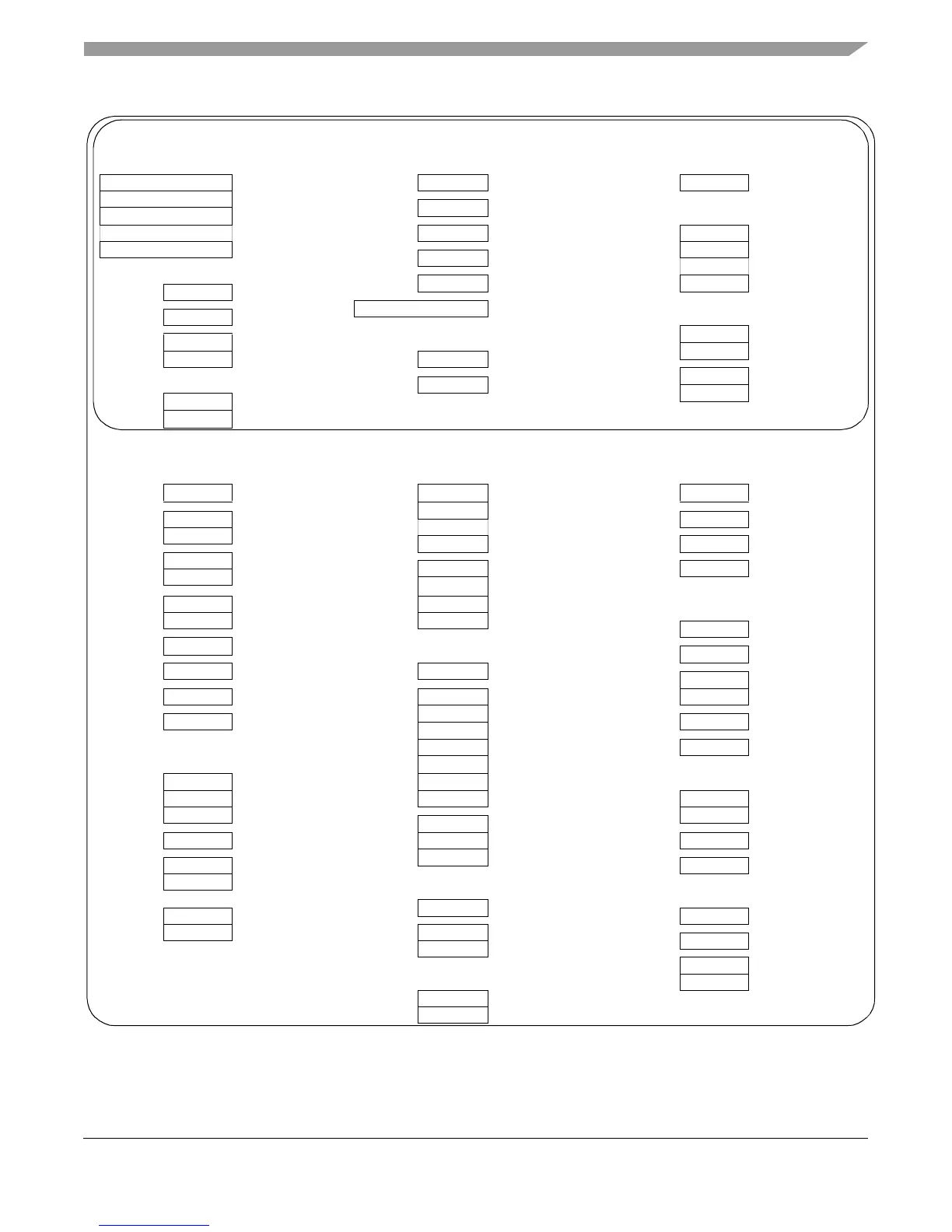

Supervisor-Level Registers

Interrupt Registers Configuration Registers

32 63 32 63 32 63

spr 63 IVPR

Interrupt vector

prefix

spr 400 IVOR0

Interrupt vector offset

registers 0–15

MSR Machine state

spr 401 IVOR1

spr 26 SRR0

Save/restore

registers 0/1

spr 1023 SVR System version

• • •

spr 27

SRR1

spr 415 IVOR15 spr 286 PIR Processor ID

spr 58 CSRR0

Critical SRR 0/1 Processor version spr 528 IVOR32

1

Interrupt vector offset

registers 32–35

spr 287 PVR

spr 59 CSRR1

spr 529

IVOR33

1

Timer/Decrementer Registers

spr 570

MCSRR0

1

Machine check

SRR 0/1

spr 530 IVOR34

1

spr 571

MCSRR1

1

spr 531 IVOR35

1

spr 22 DEC Decrementer

Exception syndrome

register

spr 62

ESR

MMU Control and Status (Read/Write)

Decrementer

auto-reload

spr 54 DECAR

MMU control and status

register 0

spr 572 MCSR

1

Machine check

syndrome register

spr 1012 MMUCSR0

1

spr 284 TBL

Time base

lower/upper

spr 573 MCAR Machine check

address register

spr 624 MAS0

1

MMU assist

registers

spr 285 TBU

spr 625 MAS1

1

spr 61 DEAR Data exception

address register

spr 340 TCR Timer control

spr 626

MAS2

1

spr 627 MAS3

1

spr 336 TSR Timer status

Debug Registers

spr 628

MAS4

1

Miscellaneous Registers

spr 308 DBCR0

Debug control

registers 0–2

spr 630

MAS6

1

Hardware

implementation

dependent 0–1

spr 309 DBCR1

spr 944

MAS7

1. 2

2

e500v2 only

spr 1008

HID0

1

spr 310

DBCR2

spr 1009

HID1

1

spr 48

PID0

Process ID

registers 0–2

spr 304

DBSR

Debug status register spr 633

PID1

1

spr 1013

BUCSR

3

3

These registers are e500-specific

Branch control and

status register

Instruction address

compare

registers 1 and 2

spr 634 PID2

1

spr 312 IAC1

spr 272–279

SPRG0–7

General SPRs 0–7

spr 313 IAC2

MMU Control and Status (Read Only)

Performance Monitor Registers

Data address

compare

registers 1 and 2

spr 1015 MMUCFG

1

MMU configuration

spr 316 DAC1 pmr 400 PMGC0

1

Global control register

spr 317 DAC2 spr 688 TLB0CFG

1

TLB configuration 0/1 pmr 16–19

PMC0–3

1

Counter registers 0–3

spr 689 TLB1CFG

pmr 144–147

PMLCa0–3

1

Local control a0–a3

L1 Cache (Read/Write)

pmr 272–275

PMLCb0–3

1

Local control b0–b3

spr 1010

L1CSR0

1

L1 Cache

Control/Status 0/1

spr 1011 L1CSR1

1

Loading...

Loading...