Register Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 2-17

access to the 64-bit alternate time base counter, which is incremented at an

implementation-defined frequency. On the e500v2, this frequency is the core frequency. The ATB

register is accessible in both user and supervisor mode.

Like the TB implementation, the ATBL register is an aliased name for ATB.

Table 2-6 describes the ATB fields.

2.6.6.1 Alternate Time Base Upper (ATBU)

The ATBU register, shown in Figure 2-8, provides read-only access to the upper 32 bits of the

alternate time base counter. It is accessible in both user and supervisor mode.

Table 2-7 describes the ATBU fields.

2.7 Interrupt Registers

Section 2.7.1, “Interrupt Registers Defined by Book E,” and Section 2.7.2, “e500-Specific

Interrupt Registers,” describe registers used for interrupt handling.

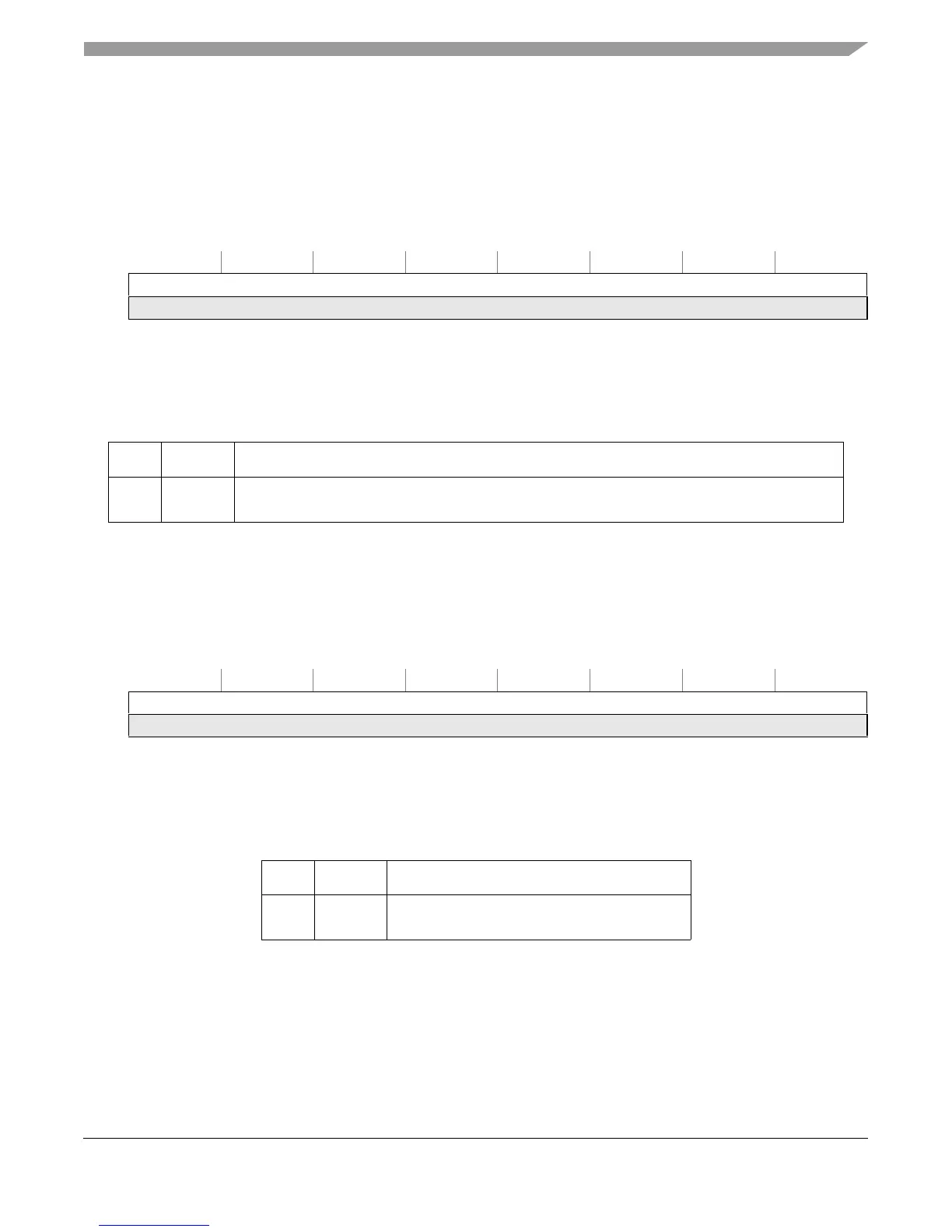

SPR 526 Access: User read-only

32 63

R ATB L U

W

Reset All zeros

Figure 2-7. Alternate Time Base Register Lower (ATBL)

Table 2-6. ATBL Field Descriptions

Bits Name Description

32–63 ATBCL Alternate time base counter lower

Lower 32 bits of the alternate time base counter

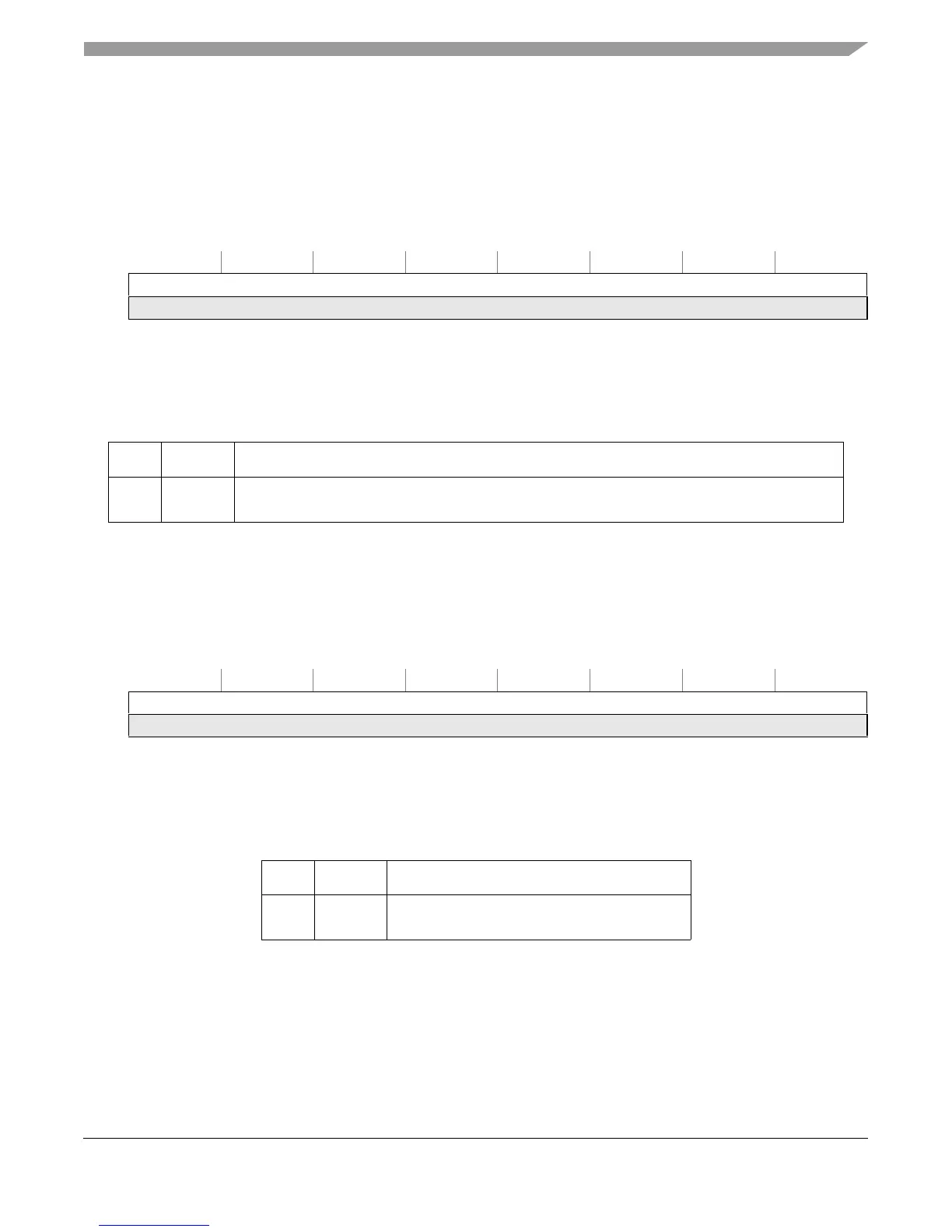

SPR 527 Access: User read-only

32 63

R AT B C U

W

Reset All zeros

Figure 2-8. Alternate Time Base Register Upper (ATBU)

Table 2-7. ATBU Field Descriptions

Bits Name Description

32–63 ATBCU Alternate time base counter upper

Upper 32 bits of the alternate time base counter

Loading...

Loading...