Interrupts and Exceptions

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 5-19

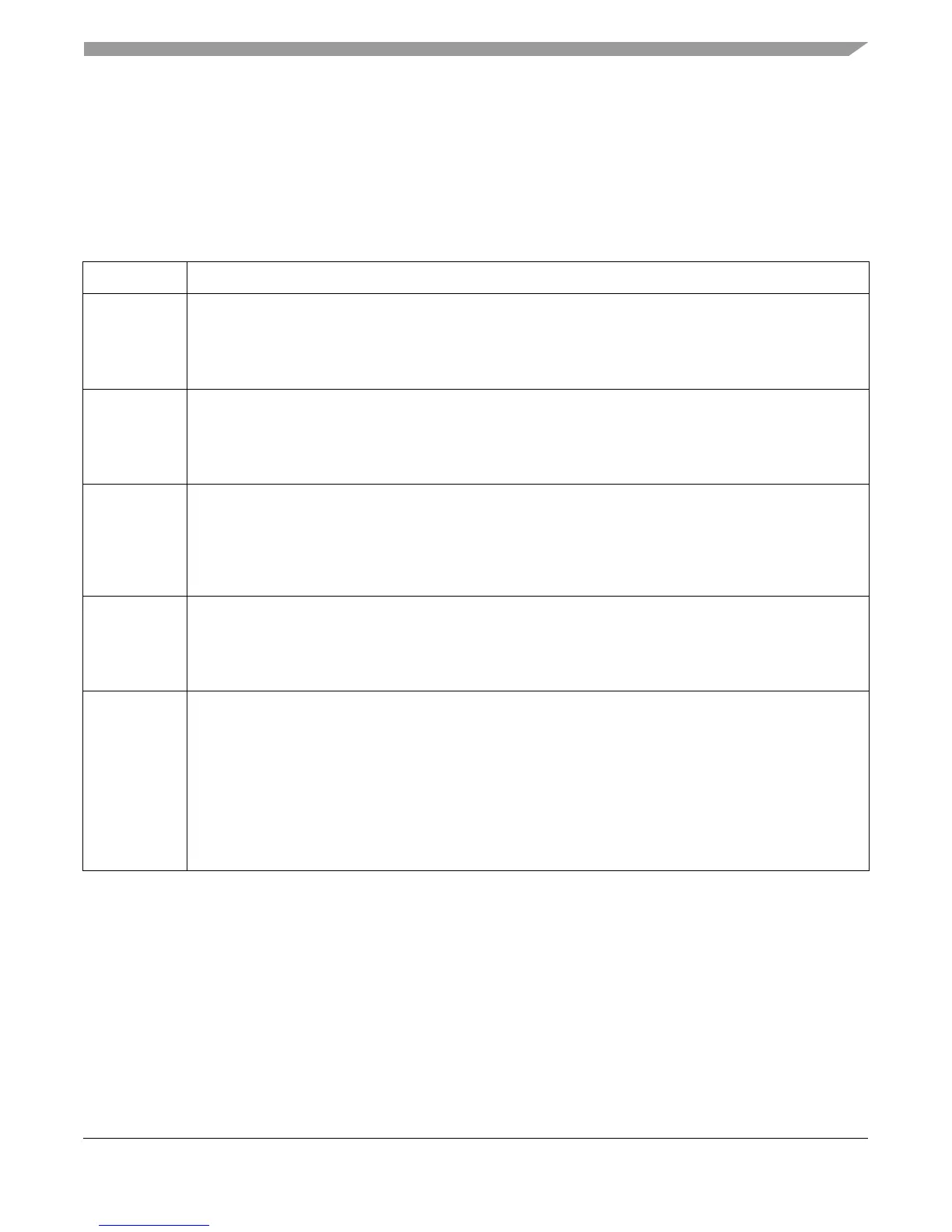

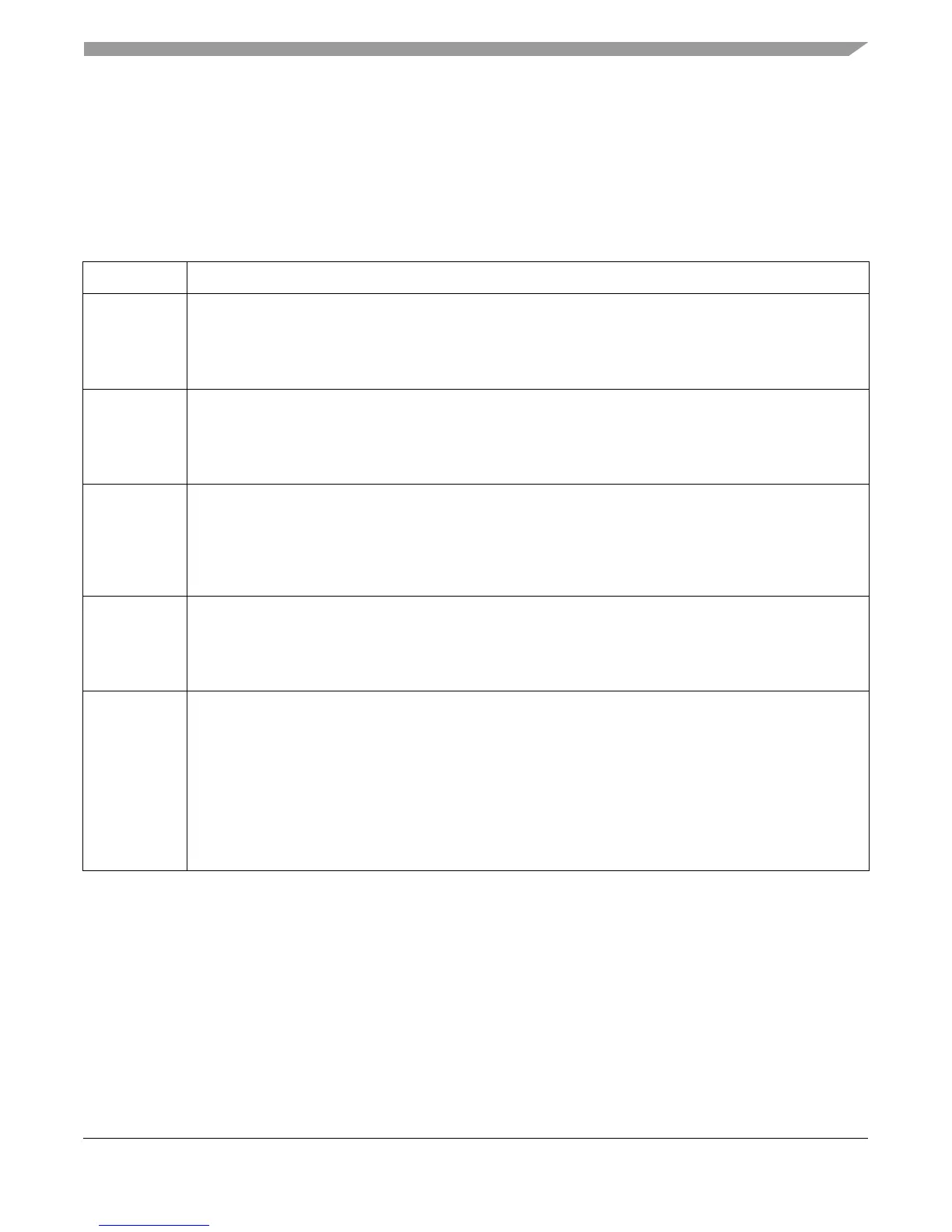

5.7.3 Data Storage Interrupt

A data storage interrupt (DSI) occurs when no higher priority exception exists and a data storage

exception is presented to the interrupt mechanism. Table 5-11 describes exception conditions for

a data storage interrupt as defined by Book E.

icbt, dcbt, dcbtst, and dcba instructions cannot cause a data storage interrupt, regardless of the

effective address.

Table 5-11. Data Storage Interrupt Exception Conditions

Exception Cause

Read access

control

exception

Occurs when either of the following conditions exists:

• In user mode (MSR[PR] = 1), a load or load-class cache management instruction attempts to access a

memory location that is not user-mode read enabled (page access control bit UR = 0).

• In supervisor mode (MSR[PR] = 0), a load or load-class cache management instruction attempts to access

a location that is not supervisor-mode read enabled (page access control bit SR = 0).

Write access

control

exception

Occurs when either of the following conditions exists:

• In user mode (MSR[PR] = 1), a store or store-class cache management instruction attempts to access a

location that is not user-mode write enabled (page access control bit UW = 0).

• In supervisor mode (MSR[PR] = 0), a store or store-class cache management instruction attempts to access

a location that is not supervisor-mode write enabled (page access control bit SW = 0).

Byte-ordering

exception

The implementation cannot access data in the byte order specified by the page’s endian attribute.

Note: The byte-ordering exception is provided to assist implementations that cannot support dynamically

switching byte ordering between consecutive accesses, the byte order for a class of accesses, or misaligned

accesses using a specific byte order.

On the e500, load/store accesses that cross a page boundary such that endianness changes cause a

byte-ordering exception.

Cache locking

exception

(EIS) The locked state of one or more cache lines has the potential to be altered. This exception is

implementation-dependent. A cache locking exception occurs with the execution of icbtls, icblc, dcbtls,

dcbtstls, or dcblc when (MSR[PR] = 1) and (MSR[UCLE] = 0). ESR is set as follows:

•For icbtls and icblc, ESR[ILK] is set.

•For dcbtls, dcbtstls, or dcblc, ESR[DLK] is set. Book E refers to this as a cache-locking exception.

Storage

synchronization

exception

Occurs when either of the following conditions exists:

• An attempt is made to execute a load and reserve or store conditional instruction from or to a location that

is write-through required or caching inhibited. (If the interrupt does not occur, the instruction executes

correctly.)

• A store conditional instruction produces an effective address for which a normal store would cause a data

storage interrupt but the processor does not have the reservation from a load and reserve instruction. Book E

states that it is implementation-dependent whether a data storage interrupt occurs. The EIS defines that the

data storage interrupt is taken.

See the section, “Atomic Update Primitives Using lwarx and stwcx.,” in the “Instruction Model” chapter of the

EREF.

Loading...

Loading...