PowerPC e500 Core Family Reference Manual, Rev. 1

2-40 Freescale Semiconductor

Register Model

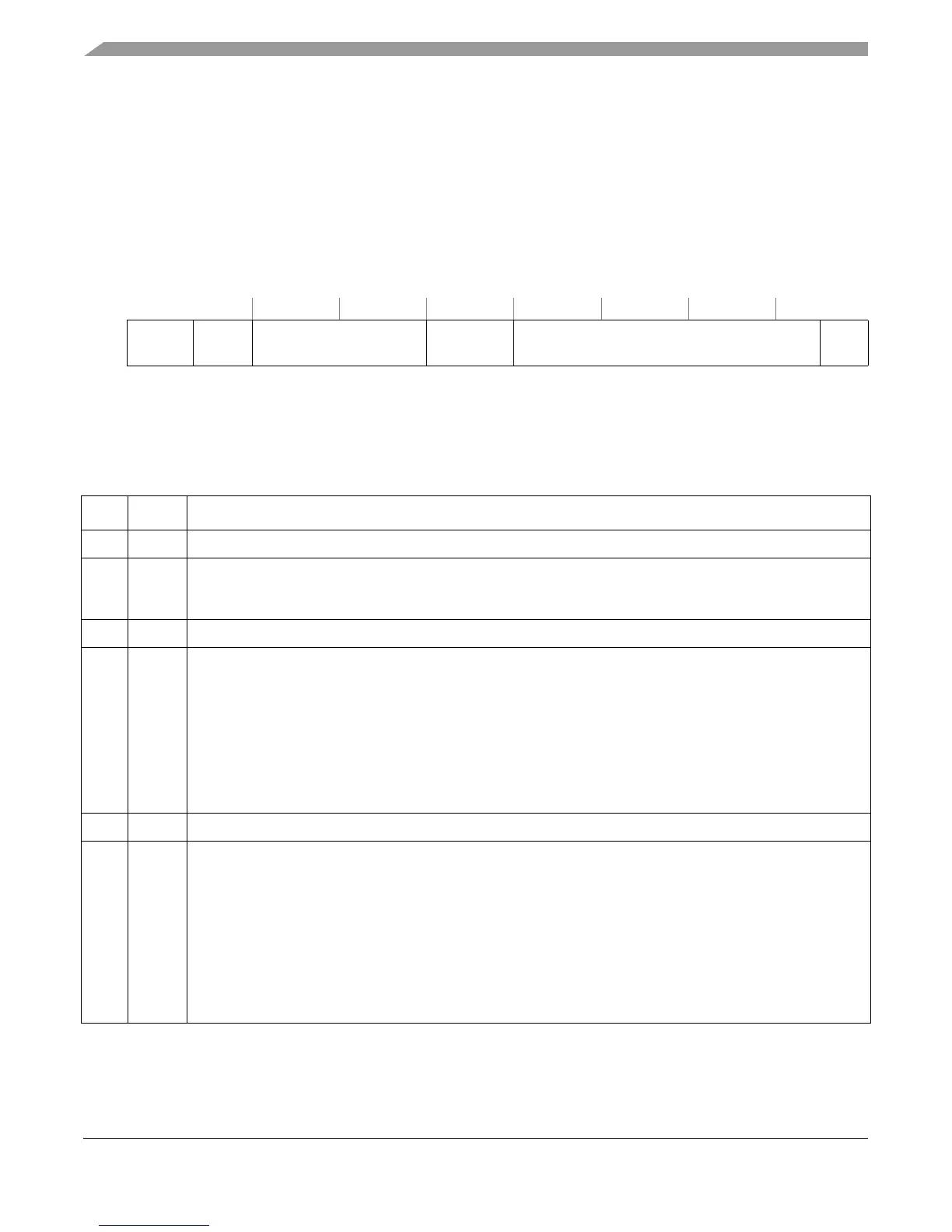

2.12.5.1 MAS Register 0 (MAS0)

Figure 2-29 shows MAS0 as it is implemented on the e500. For the e500, TLB0 is two-way set

associative, so bits 45–51 of the effective address are used to index into TLB0. ESEL then

identifies which of the two indexed entries is to be referenced by the TLB operation (ESEL selects

the way). Writing to MAS0 requires synchronization, as described in Section 2.16,

“Synchronization Requirements for SPRs.”

The MAS0 fields are described in Table 2-24.

SPR 624 Access: Supervisor-only

32 34 35 36 43 44 47 48 61 62 63

R

— TLBSEL — ESEL — NV

W

Reset All zeros

Figure 2-29. MAS Register 0 (MAS0)

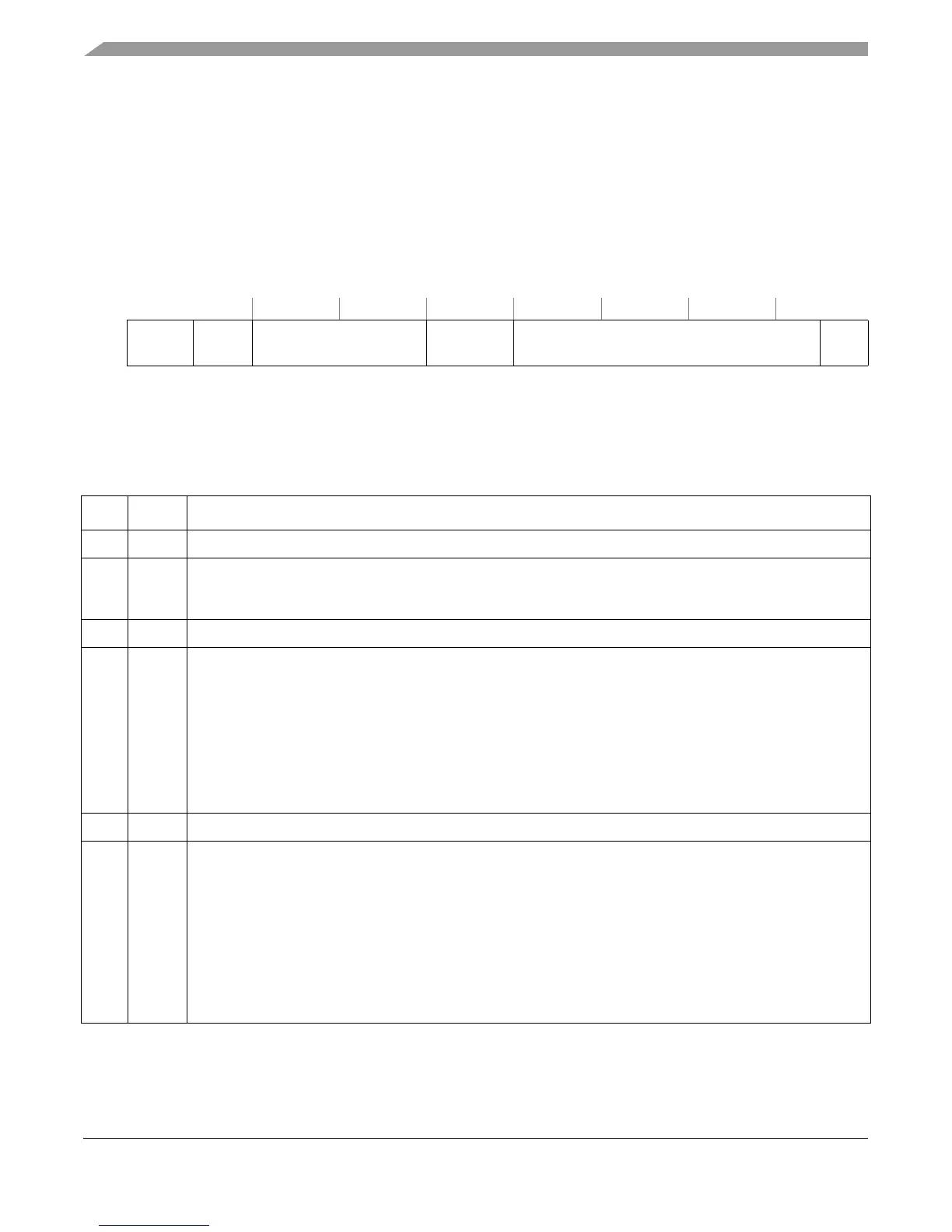

Table 2-24. MAS0 Field Descriptions—MMU Read/Write and Replacement Control

Bit Name Comments or Function when Set

32–34 — Reserved, should be cleared.

35 TLBSEL Selects TLB for access.

0TLB0

1TLB1

36–43 — Reserved, should be cleared.

44–47 ESEL Entry select. Number of the entry in the selected array to be used for tlbwe. Updated on TLB error exceptions

(misses) and tlbsx hit and miss cases. Only certain bits are valid, depending on the array selected in TLBSEL.

Other bits should be 0.

For the e500, ESEL serves as the way select for the corresponding TLB as follows:

When TLBSEL = 00 (TLB0 selected), bits 46–47 are used (and bits 44–45 should be cleared). This field selects

between way 0, 1, 2, or 3 of TLB0. EA bits 45–51 from MAS2[EPN] are used to index into the TLB to further

select the entry for the operation. Note that for the e500v1, bit 47 selects either way 0 or way 1, and bit 46 should

remain cleared.

When TLBSEL = 01 (TLB1 selected), all four bits are used to select one of 16 entries in the array.

48–61 — Reserved, should be cleared.

62–63 NV Next victim. (Note that the Freescale standard allows NV to be as large as 12-bits on other implementations.)

Can be used to identify the next victim to be targeted for a TLB miss replacement operation for those TLBs that

support the NV field. If the TLB selected by MAS0[TLBSEL] does not support the NV field, then this field is

undefined. The specific meaning of this field is implementation-dependent.

For the e500, NV is the next victim value to be written to TLB0[NV] on execution of tlbwe. This field is also

updated on TLB error exceptions (misses), tlbsx hit and miss cases, and on execution of tlbre.

This field is updated based on the calculated next victim value for TLB0 (based on the round-robin replacement

algorithm, described in Section 12.3.2.2, “Replacement Algorithms for L2 MMU”). Note that for the e500v1, bit

62 should remain cleared and only bit 63 has significance.

Note that this field is not defined for operations that specify TLB1 (when TLBSEL = 01).

Loading...

Loading...