L1 Caches

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 11-25

11.6.2 L1 Cache Block Replacement

When a new block needs to be placed in the instruction or data cache, the

pseudo–least-recently-used (PLRU) replacement algorithm is used. Note that data cache

replacement selection is performed at reload time and not when the miss occurs. Instruction cache

replacement selection occurs when an instruction cache miss is first recognized.

When a cache line is accessed, it is tagged as the most-recently-used line of the set. When a miss

occurs, if all lines in the set are valid (occupied), the least-recently-used line is replaced with the

new data. The PLRU bits in the cache are updated each time a cache hit occurs based on the

most-recently-used cache line.

Modified data to be replaced is written into a DWB and eventually is written back to main memory.

Data load or write-back store accesses that miss in the L1 data cache function similarly to L1

instruction cache misses. They cause a new line to be allocated on a PLRU basis, provided the

cache is not completely locked or disabled.

Note that modified data in the replacement line of any cache can cause a castout to occur to the

CCB. In all such cases, the castout is not initiated until new data is ready to be loaded.

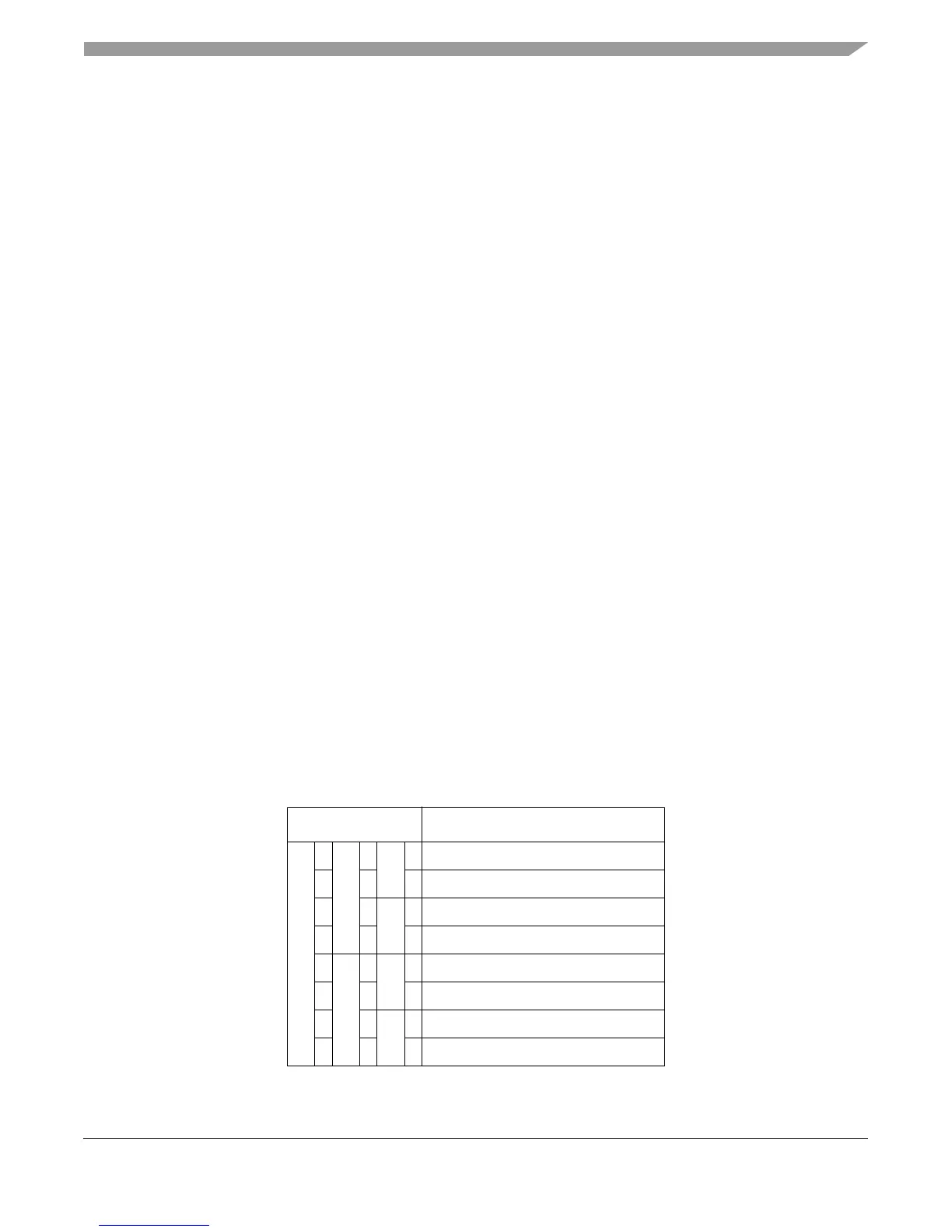

11.6.2.1 PLRU Replacement

Block replacement is performed using a binary decision tree, PLRU algorithm. There is an

identifying bit for each cache way, L[0–7]. There are seven PLRU bits, B[0–6] for each set in the

cache to determine the line to be cast out (replacement victim). The PLRU bits are updated when

a new line is allocated or replaced and when there is a hit in the set.

This algorithm prioritizes the replacement of invalid entries over valid ones (starting with way 0).

Otherwise, if all ways are valid, one is selected for replacement according to the PLRU bit

encodings shown in Table 11-8.

Table 11-8. L1 PLRU Replacement Way Selection

PLRU Bits Way Selected for Replacement

B0 0 B1 0 B3 0L0

001 L1

01B4 0L2

011 L3

1 B2 0 B5 0L4

101 L5

11B6 0L6

111 L7

Loading...

Loading...