PowerPC e500 Core Family Reference Manual, Rev. 1

12-28 Freescale Semiconductor

Memory Management Units

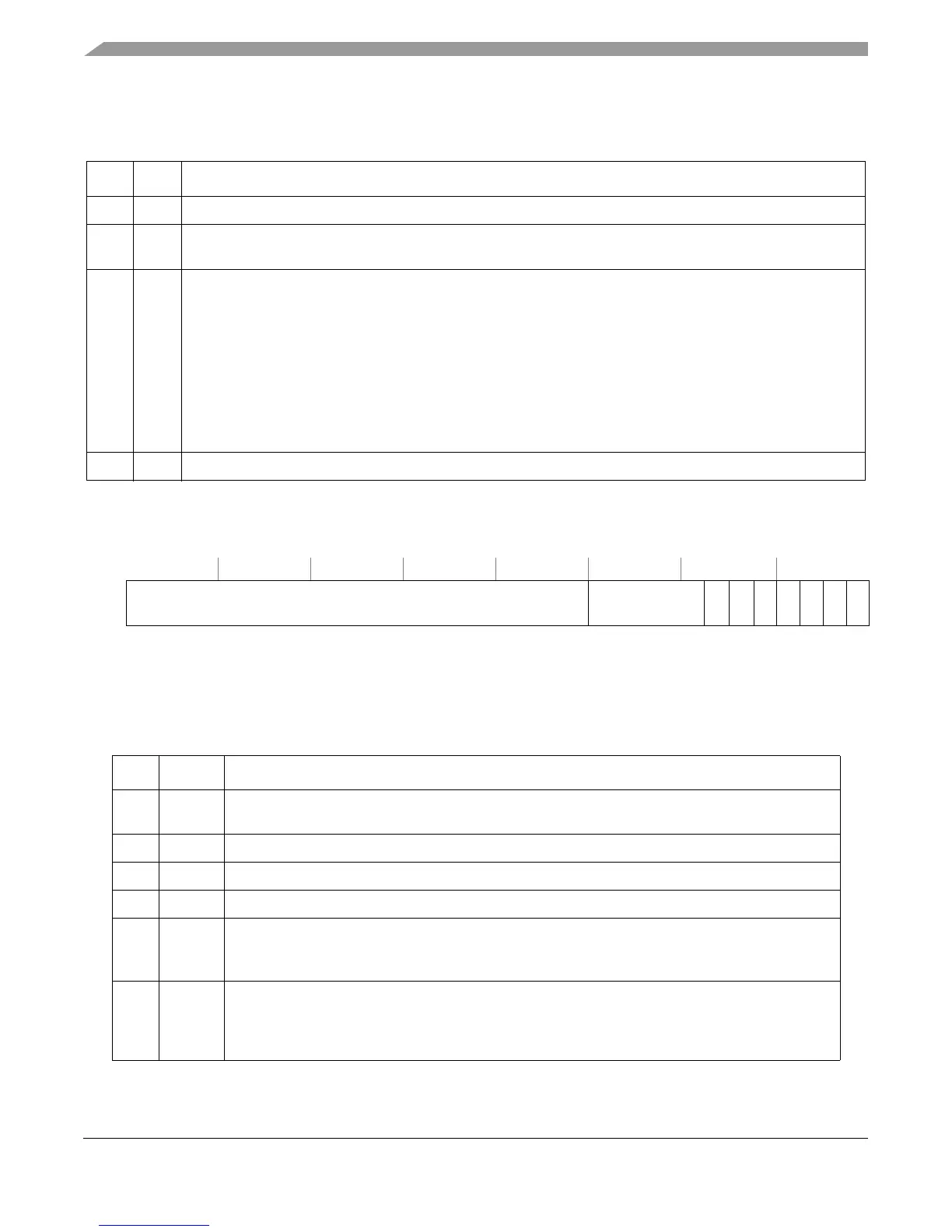

Figure 12-13 describes the format of MAS2 on the e500 core complex.

Table 12-10 shows the core complex MAS2 bit definitions.

48–50 — Reserved, should be cleared.

51 TS Translation space. This bit is compared with the IS or DS fields of the MSR (depending on the type of access)

to determine if this TLB entry may be used for translation.

52–55 TSIZE Translation size. Defines the page size of the TLB entry. For TLB arrays that contain fixed-size TLB entries, this

field is ignored. For variable page size TLB arrays, the page size is 4

TSIZE

Kbytes. Note that although the

Freescale Book E standard supports all 16 page sizes defined in Book E, the e500 only supports the following

page sizes:

0001 4 Kbyte

0010 16 Kbyte

0011 64 Kbyte

0100 256 Kbyte

0101 1 Mbyte

0110 4 Mbyte

0111 16 Mbyte

1000 64 Mbyte

1001 256 Mbyte

1010 1 Gbyte

1011 4 Gbyte

56–63 — Reserved, should be cleared.

SPR 626 Access: Supervisor-only

32 51 52 56 57 58 59 60 61 62 63

R

EPN —X0X1WIMGE

W

Reset All zeros

Figure 12-13. MAS Register 2 (MAS2)

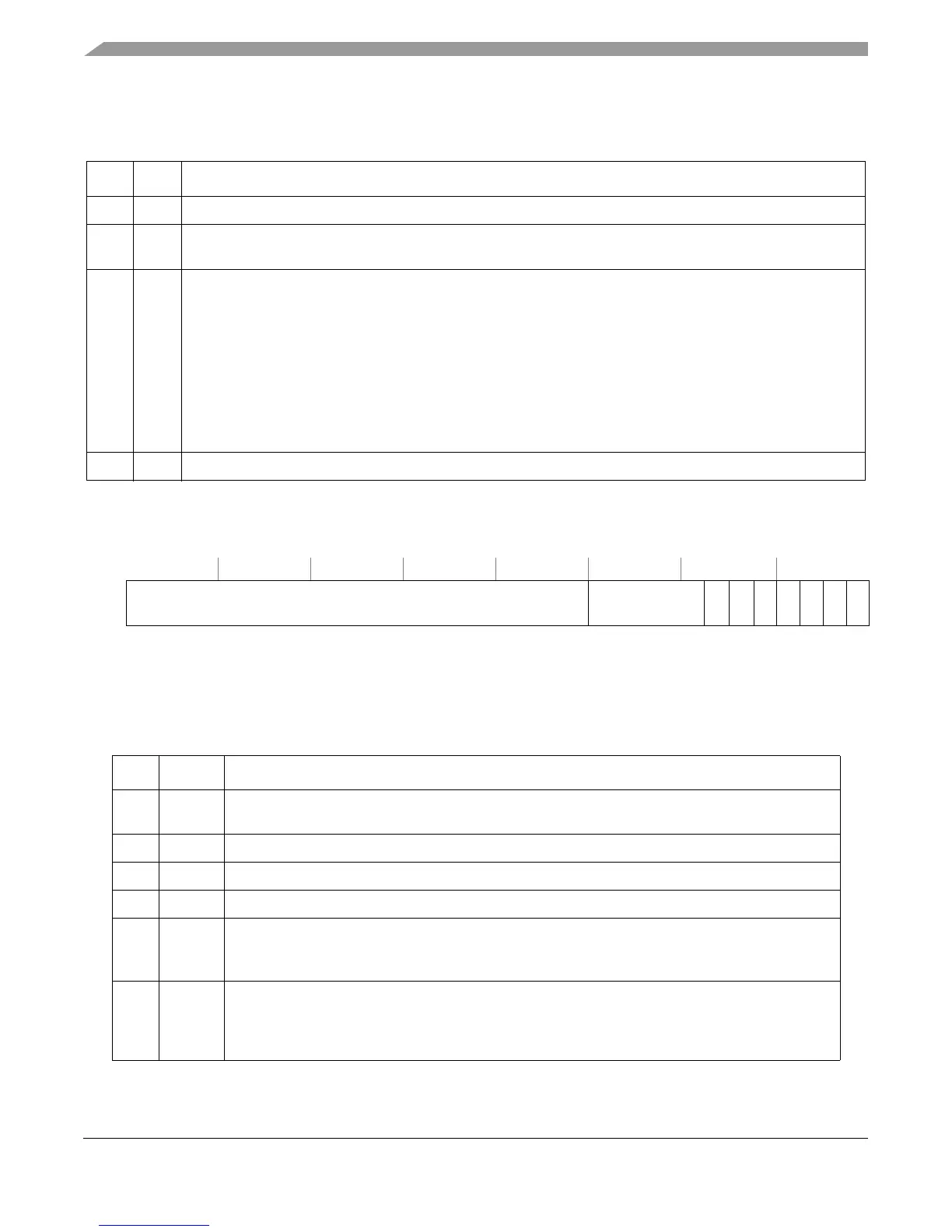

Table 12-10. MAS2 Field Descriptions—EPN and Page Attributes

Bits Name Description

32–51 EPN Effective page number. Depending on page size, only the bits associated with a page boundary are

valid. Bits that represent offsets within a page are ignored and should be cleared.

52–56 — Reserved, should be cleared.

57 X0 Implementation-dependent page attribute

58 X1 Implementation-dependent page attribute

59 W Write-through

0 This page is considered write-back with respect to the caches in the system.

1 All stores performed to this page are written through the caches to main memory.

60 I Caching-inhibited

0 Accesses to this page are considered cacheable.

1 The page is considered caching-inhibited. All loads and stores to the page bypass the caches and

are performed directly to main memory.

Table 12-9. MAS1 Field Descriptions—Descriptor Context and Configuration

Control (continued)

Bits Name Descriptions

Loading...

Loading...