Execution Timing

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 4-31

4.6 Instruction Latency Summary

Instruction timing is shown in Table 4-3 through Table 4-7. The latency tables use the following

conventions:

• Pipelined load/store and floating-point instructions are shown with cycles of total latency

and throughput cycles separated by a colon.

• Floating-point instructions with a single entry in the cycles column are not pipelined.

Integer divide instructions are also not pipelined with other divides.

Table 4-3 through Table 4-7 list latencies associated with instructions executed by each execution

unit. Figure 4-3 describes branch instruction latencies.

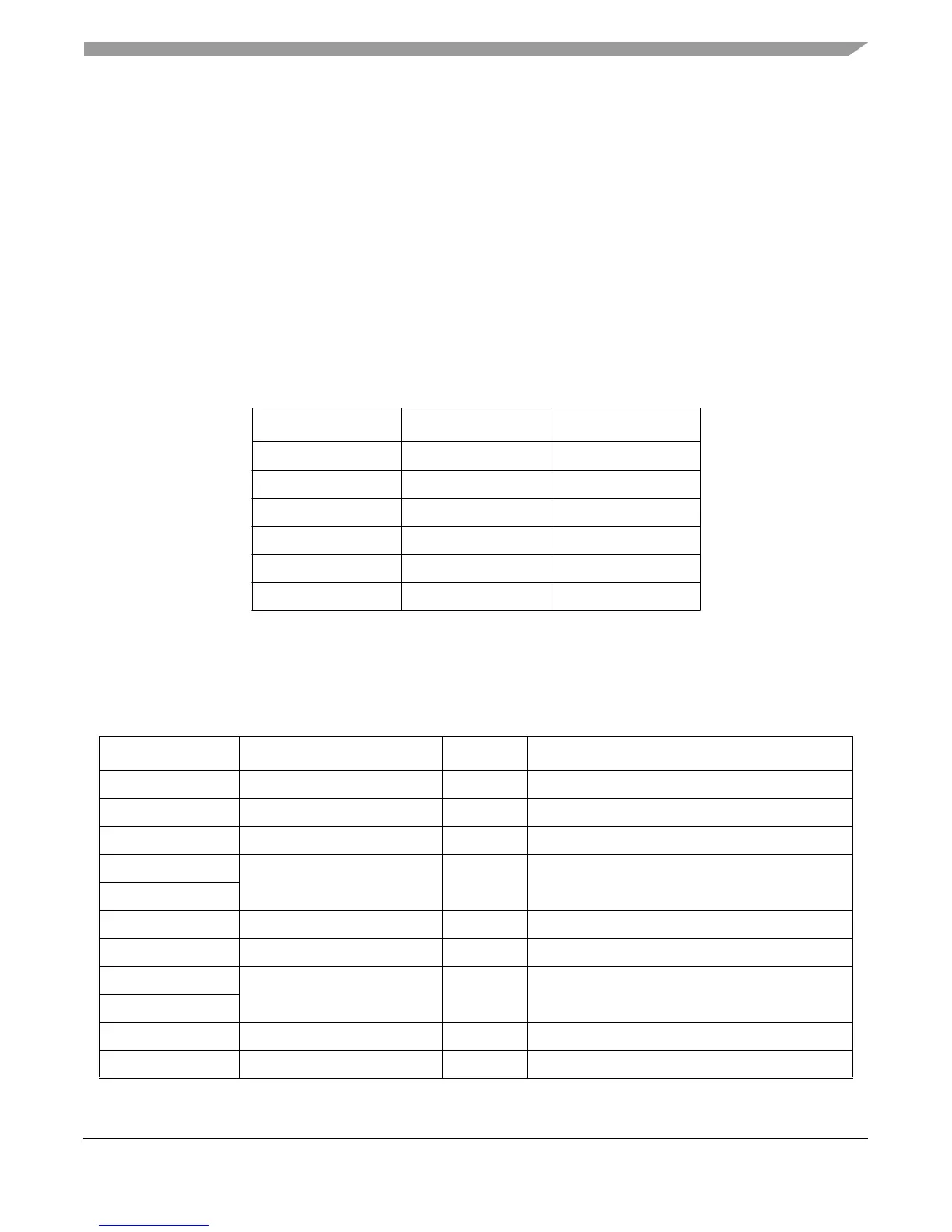

Table 4-4 lists system operation instruction latencies. The instructions in Table 4-4 are grouped by

the serialization they require. Except where otherwise noted, throughput is the same for the

instructions within each serialization grouping.

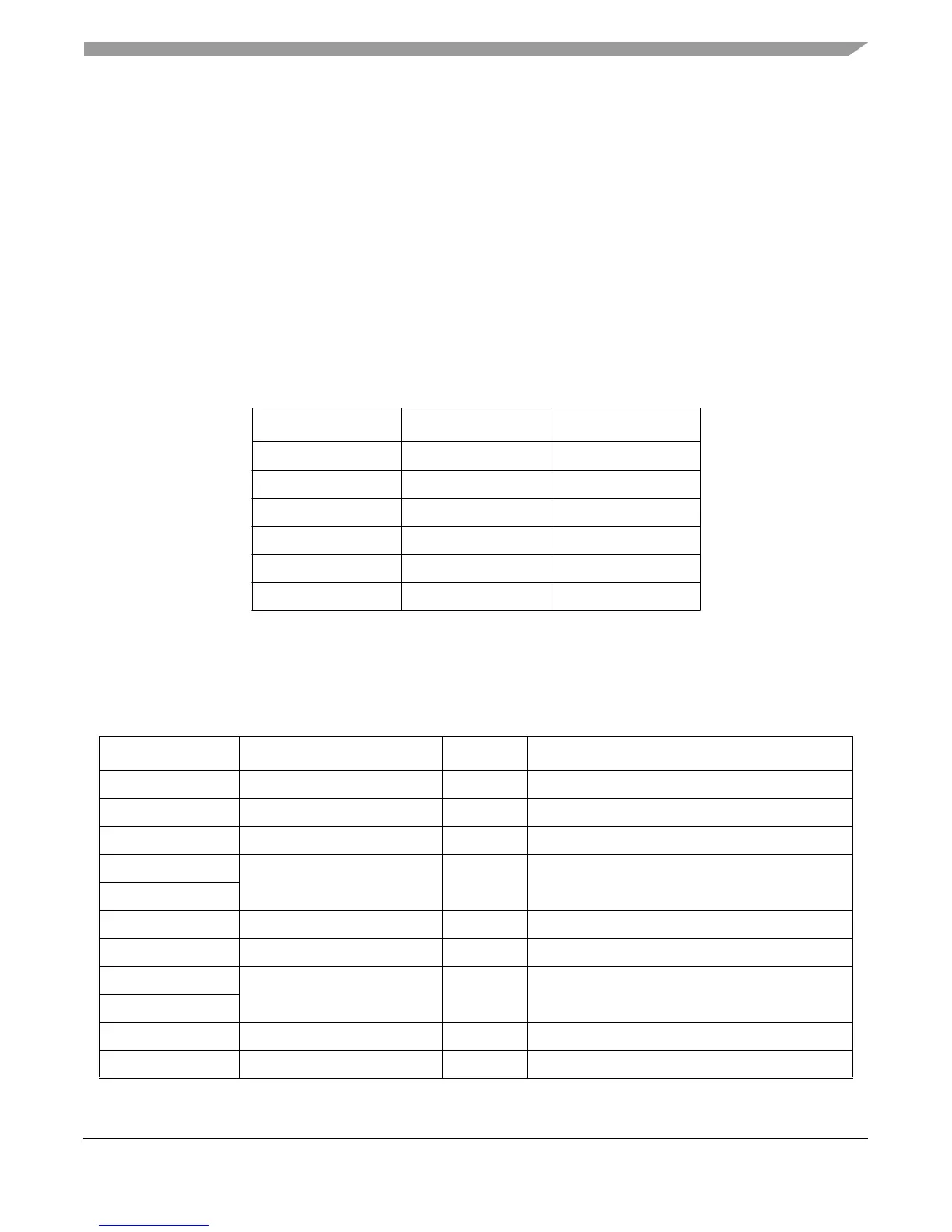

Table 4-3. Branch Operation Execution Latencies

Mnemonic Cycles Serialization

bbelr 1 Pre- and postsync

bblels 1 Pre- and postsync

bcctr[l]1 —

bclr[l]1 —

bc[l][a]1 —

b[l][a]1 —

Table 4-4. System Operation Instruction Execution Latencies

Mnemonic Serialization

1

Unit Cycles

isync Refetch —

2

0

mbar Store LSU 3:1

msync Store and postsync. LSU Latency depends on bus response time.

mfcr Move-from SU1 only 4

mfspr[XER]

mfmsr None SU1 4

mfpmr None SU1 only 4

7

mfspr[CTR]

3, 4

None SU1 or SU2 1

mfspr[LR]

3,5

mfspr[DBSR] Presync, postsync SU1 only 4

mfspr[SSCR] Presync SU1 only 4

Loading...

Loading...