PowerPC e500 Core Family Reference Manual, Rev. 1

3-8 Freescale Semiconductor

Instruction Model

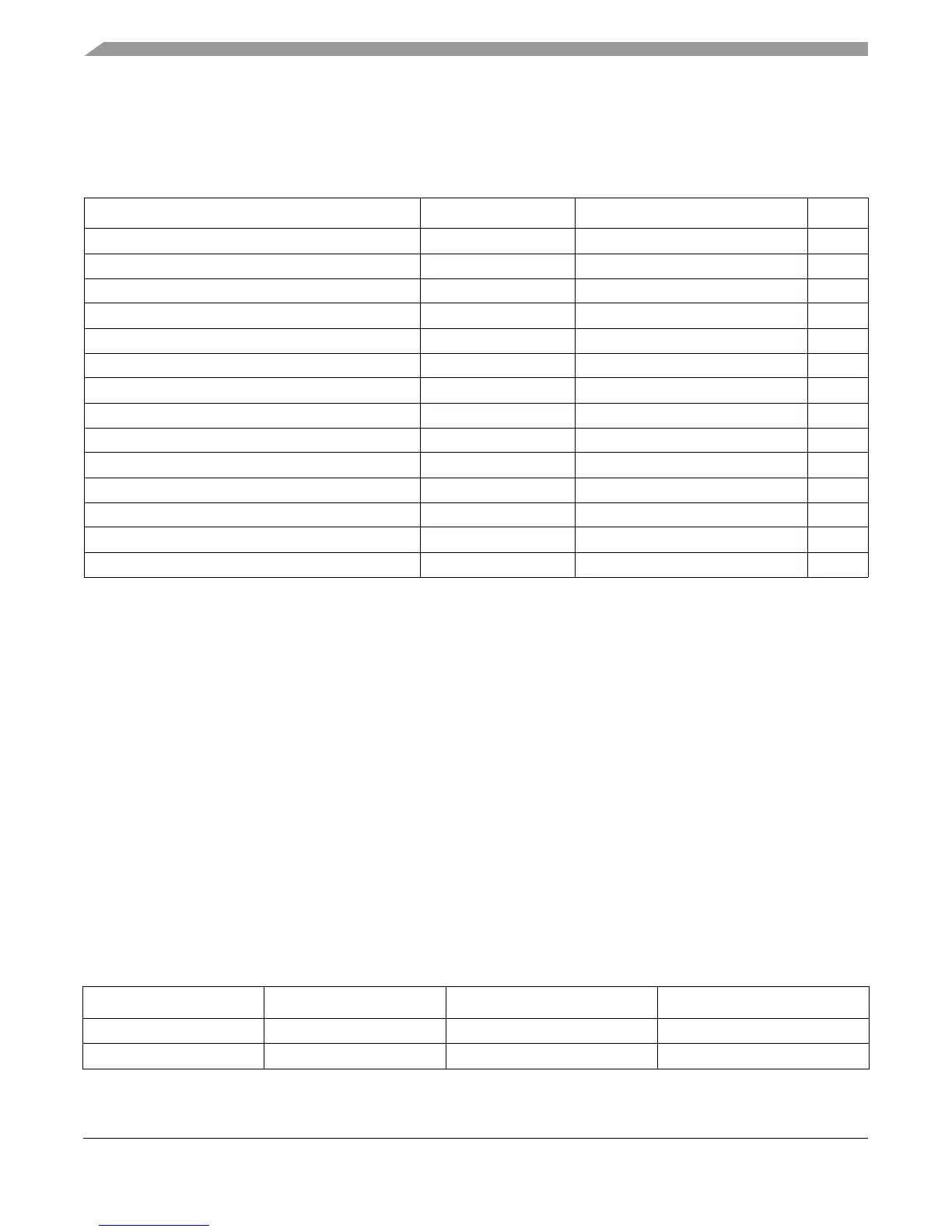

Table 3-3 identifies the software synchronization requirements for data access for all

context-altering instructions.

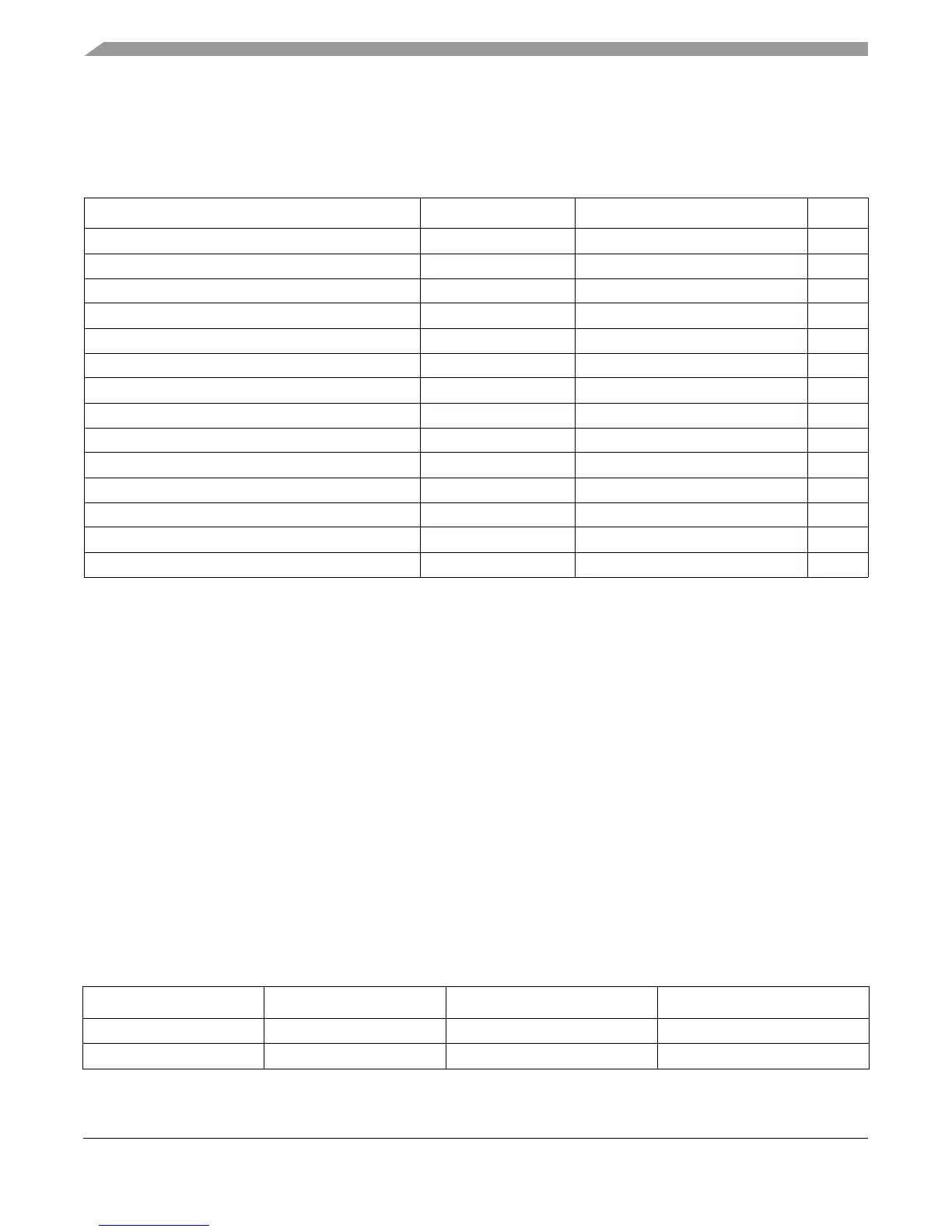

3.2.3.1 Synchronization Requirements for e500-Specific SPRs

Software requirements for synchronization before and after accessing certain SPRs are shown in

Table 3-4. Except for these registers, there are no synchronization requirements for accessing

SPRs beyond those stated in Book E and described in Section 3.2.3, “Synchronization

Requirements.”

Table 3-3. Data Access Synchronization Requirements

Context Altering Instruction or Event Required Before Required After Notes

Interrupt None None —

rfi None None —

rfci None None —

sc None None —

mtmsr (PR) None CSI

1

1

CSI indicates any context-synchronizing instruction (that is, sc, isync, rfci, or rfi).

—

mtmsr (ME) None CSI

12

2

A context-synchronizing instruction is required after altering MSR[ME] to ensure that the alteration takes effect for subsequent

machine check interrupts, which may not be recoverable and therefore may not be context-synchronizing.

mtmsr (DS) None CSI

1

—

mtmsr (WE) msync isync

3

3

See Section 6.4.1, “Software Considerations for Power Management.”

mtspr (DAC1, DAC2) — —

4

4

Synchronization requirements for changing any of the debug facility registers are implementation dependent.

mtspr (DBCR0, DBCR2) — —

4

mtspr (DBSR) — —

4

mtspr (PID) CSI

1

CSI

1

—

tlbivax CSI

1

CSI

1

and possibly msync

5,6

5

For data accesses, the context-synchronizing instruction before tlbwe or tlbivax ensures that all memory accesses due to

preceding instructions have completed to a point at which they have reported all exceptions they will cause.

6

The context-synchronizing instruction after tlbwe or tlbivax ensures that subsequent accesses (data and instruction) use the

updated value in any TLB entries affected. It does not ensure that all accesses previously translated by TLB entries being

updated have completed with respect to memory; if these completions must be ensured, tlbwe or tlbivax must be followed by

an msync and by a context-synchronizing instruction.

tlbwe CSI

1

CSI

1

and possibly msync

5, 6

Table 3-4. Synchronization Requirements for e500-Specific SPRs

Registers Instruction Instruction Required Before Instruction Required After

BBEAR mtspr bbear None isync

BBTAR mtspr bbtar None isync

Loading...

Loading...