Register Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 2-47

2.13.1.3 Debug Control Register 2 (DBCR2)

The e500 implements DBCR2 as it is defined by the Book E architecture, except as follows:

• DAC1ER and DAC2ER values of 01 are reserved.

• DVC1M, DVC2M, DVC1BE, and DVC2BE (DBCR[44–63]) are not implemented.

Figure 2-36 shows the DBCR2.

Table 2-33 provides bit definitions for DBCR2.

2.13.2 Debug Status Register (DBSR)

The DBSR provides status information for debug events and for the most recent processor reset.

The e500 implements the DBSR as it is defined by the Book E architecture, with the following

exceptions:

• It does not implement IAC3 and IAC4 (DBSR[42–43]).

• Implementation-specific events that cause an unconditional debug event are defined in

Table 2-34 (DBSR[UDE]).

• The MRR field is affected by the e500 definition of the HRESET signal, as defined in

Table 2-34.

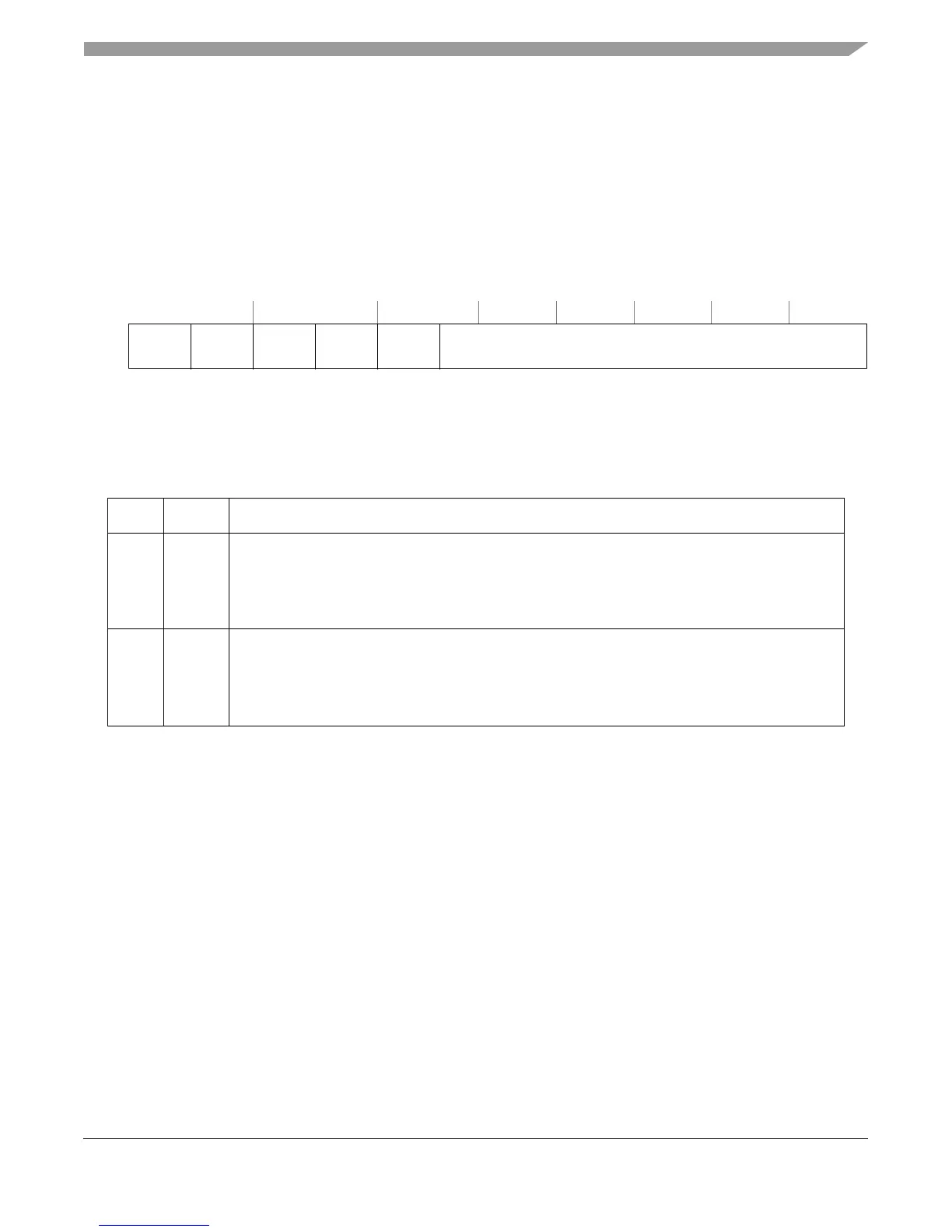

SPR 310 Access: Supervisor-only

32 33 34 35 36 37 38 39 40 41 42 63

R

DAC1US DAC1ER DAC2US DAC2ER

DAC12M —

W

Reset All zeros

Figure 2-36. Debug Control Register 2 (DBCR2)

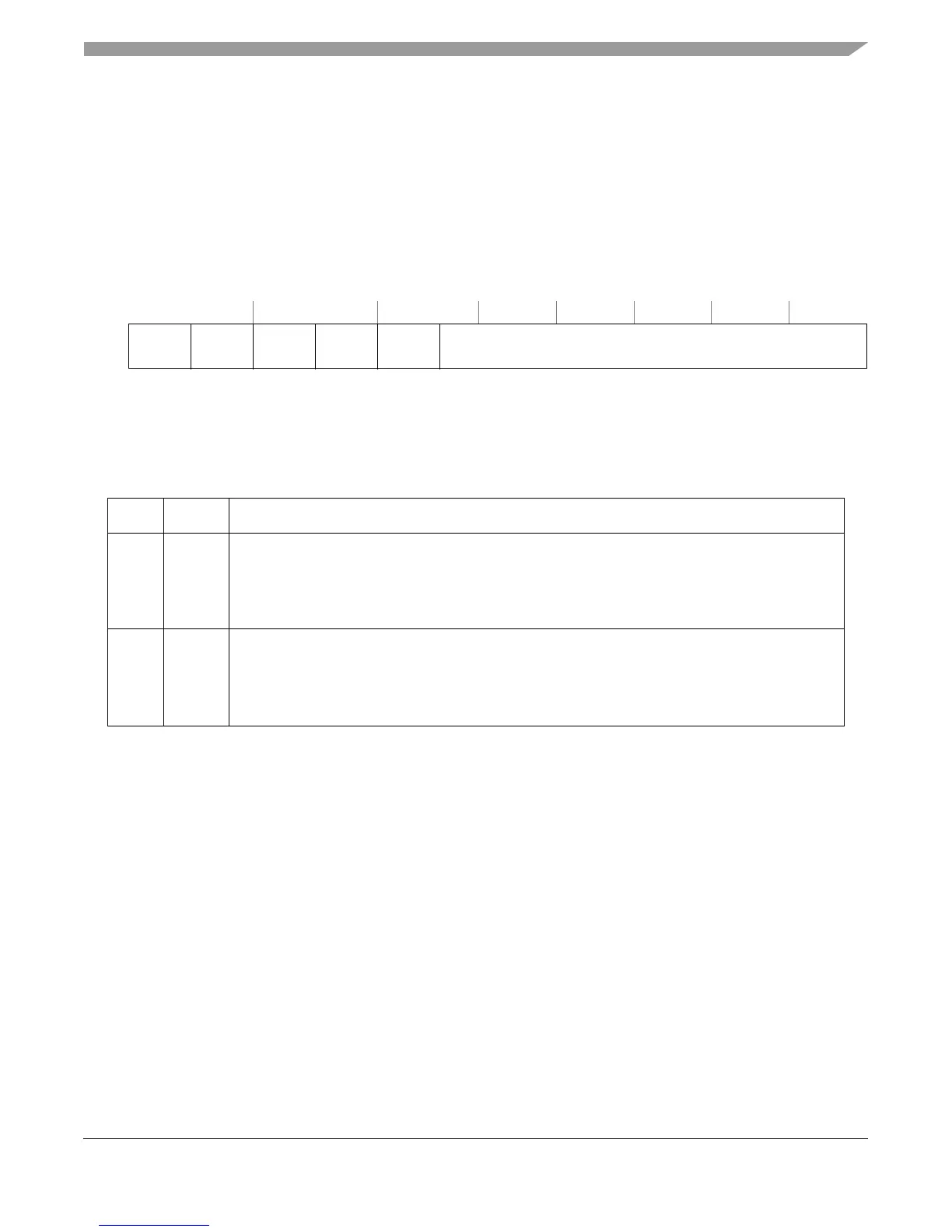

Table 2-33. DBCR2 Implementation-Specific Field Descriptions

Bits Name Description

34–35 DAC1ER Data address compare 1 effective/real mode

00 DAC1 debug events are based on effective addresses.

01 Reserved on the e500.

10 DAC1 debug events are based on effective addresses and can occur only if MSR[DS]=0.

11 DAC1 debug events are based on effective addresses and can occur only if MSR[DS]=1.

38–39 DAC2ER Data address compare 2 effective/real mode

00 DAC2 debug events are based on effective addresses.

01 Reserved on the e500.

10 DAC2 debug events are based on effective addresses and can occur only if MSR[DS]=0.

11 DAC2 debug events are based on effective addresses and can occur only if MSR[DS]=1.

Loading...

Loading...