Performance Monitor

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 7-5

7.2.2 User Global Control Register 0 (UPMGC0)

The contents of PMGC0 are reflected to UPMGC0, which can be read by user-level software.

UPMGC0 can be read with the mfpmr instruction using PMR384.

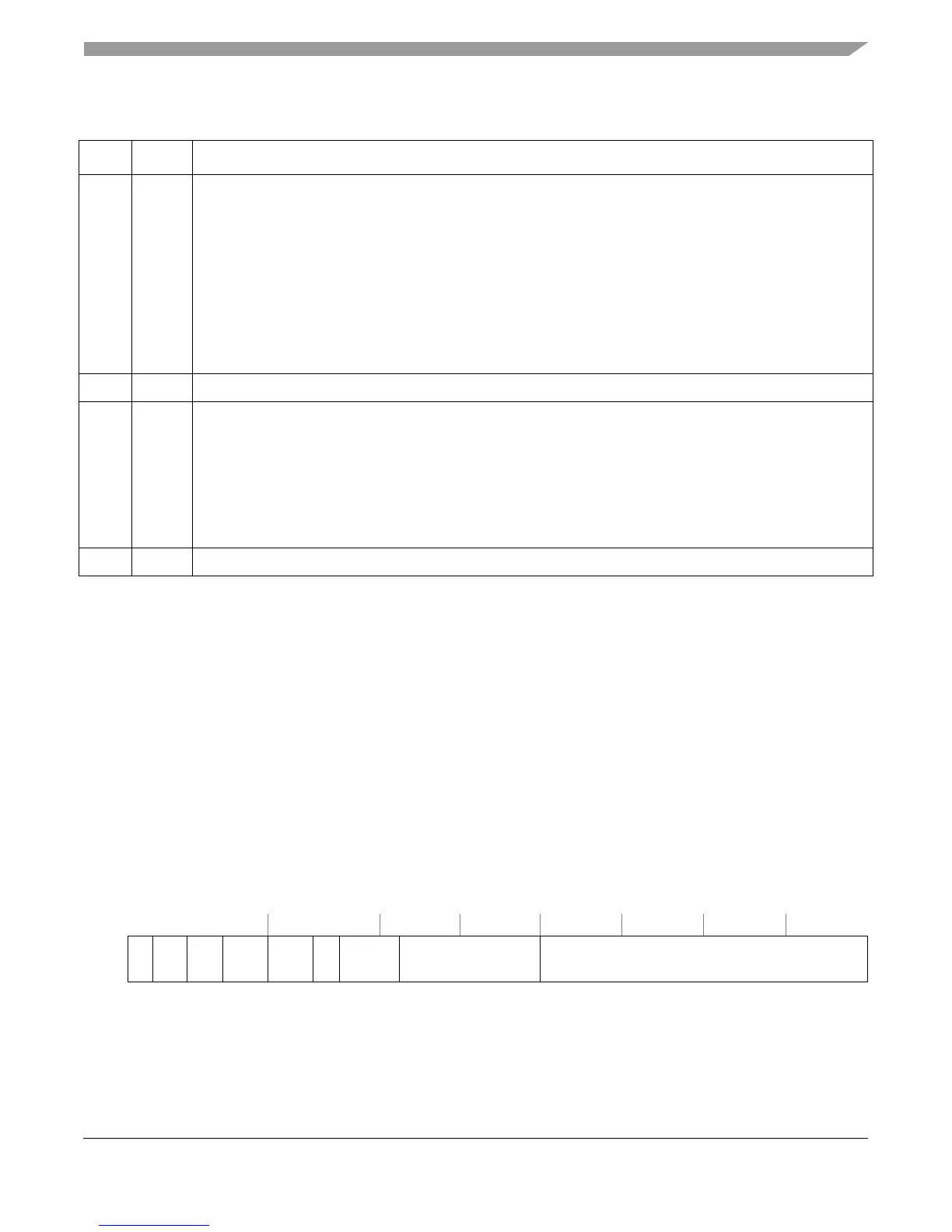

7.2.3 Local Control A Registers (PMLCa0–PMLCa3)

The local control A registers (PMLCa0–PMLCa3) function as event selectors and give local

control for the corresponding performance monitor counters. PMLCa works with the

corresponding PMLCb register. PMLCa registers are shown in Figure 7-2.

51–52 TBSEL Time base selector. Selects the time base bit that can cause a time base transition event (the event occurs

when the selected bit changes from 0 to 1).

00 TB[63] (TBL[31])

01 TB[55] (TBL[23])

10 TB[51] (TBL[19])

11 TB[47] (TBL[15])

Time base transition events can be used to periodically collect information about processor activity. In

multiprocessor systems in which TB registers are synchronized across processors, these events can be used

to correlate performance monitor data obtained by the several processors. For this use, software must specify

the same TBSEL value for all processors in the system. Time-base frequency is implementation-dependent, so

software should invoke a system service program to obtain the frequency before choosing a TBSEL value.

53–54 — Reserved, should be cleared.

55 TBEE Time base transition event exception enable

0 Exceptions from time base transition events are disabled.

1 Exceptions from time base transition events are enabled. A time base transition is signalled to the

performance monitor if the TB bit specified in PMGC0[TBSEL] changes from 0 to 1. Time base transition

events can be used to freeze counters (PMGC0[FCECE]) or signal an exception (PMGC0[PMIE]).

Changing PMGC0[TBSEL] while PMGC0[TBEE] is enabled may cause a false 0 to 1 transition that signals

the specified action (freeze, exception) to occur immediately. Although the interrupt signal condition may

occur with MSR[EE] = 0, the interrupt cannot be taken until MSR[EE] = 1.

56–63 — Reserved, should be cleared.

PMLCa0 (PMR144)

PMLCa1 (PMR145)

PMLCa2 (PMR146)

PMLCa3 (PMR147)

UPMLCa0 (PMR128)

UPMLCa1 (PMR129)

UPMLCa2 (PMR130)

UPMLCa3 (PMR131)

Access: PMLCa0–PMLCa3: Supervisor-only

UPMLCa0–UPMLCa3: Supervisor/user read-only

32 33 34 35 36 37 38 40 41 47 48 63

R

FC FCS FCU FCM1 FCM0 CE

— EVENT —

W

Reset All zeros

Figure 7-2. Local Control A Registers (PMLCa0–PMLCa3)/

User Local Control A Registers (UPMLCa0–UPMLCa3)

Table 7-3. PMGC0 Field Descriptions (continued)

Bits Name Description

Loading...

Loading...