PowerPC e500 Core Family Reference Manual, Rev. 1

9-2 Freescale Semiconductor

Timer Facilities

functions. Software may select one of four bits in the TB to serve as the fixed-interval timer.

Which bits may be selected depends on the implementation.

• The watchdog timer is also a selected bit of the TB, which provides a means of signalling

a critical class exception whenever the selected bit transitions from 0 to 1. In addition, if

software does not respond in time to the initial exception (by clearing the associated status

bits in the TSR before the next expiration of the watchdog timer interval), then a watchdog

timer-generated processor reset may result, if so enabled. The watchdog timer is typically

used to provide a system error recovery function.

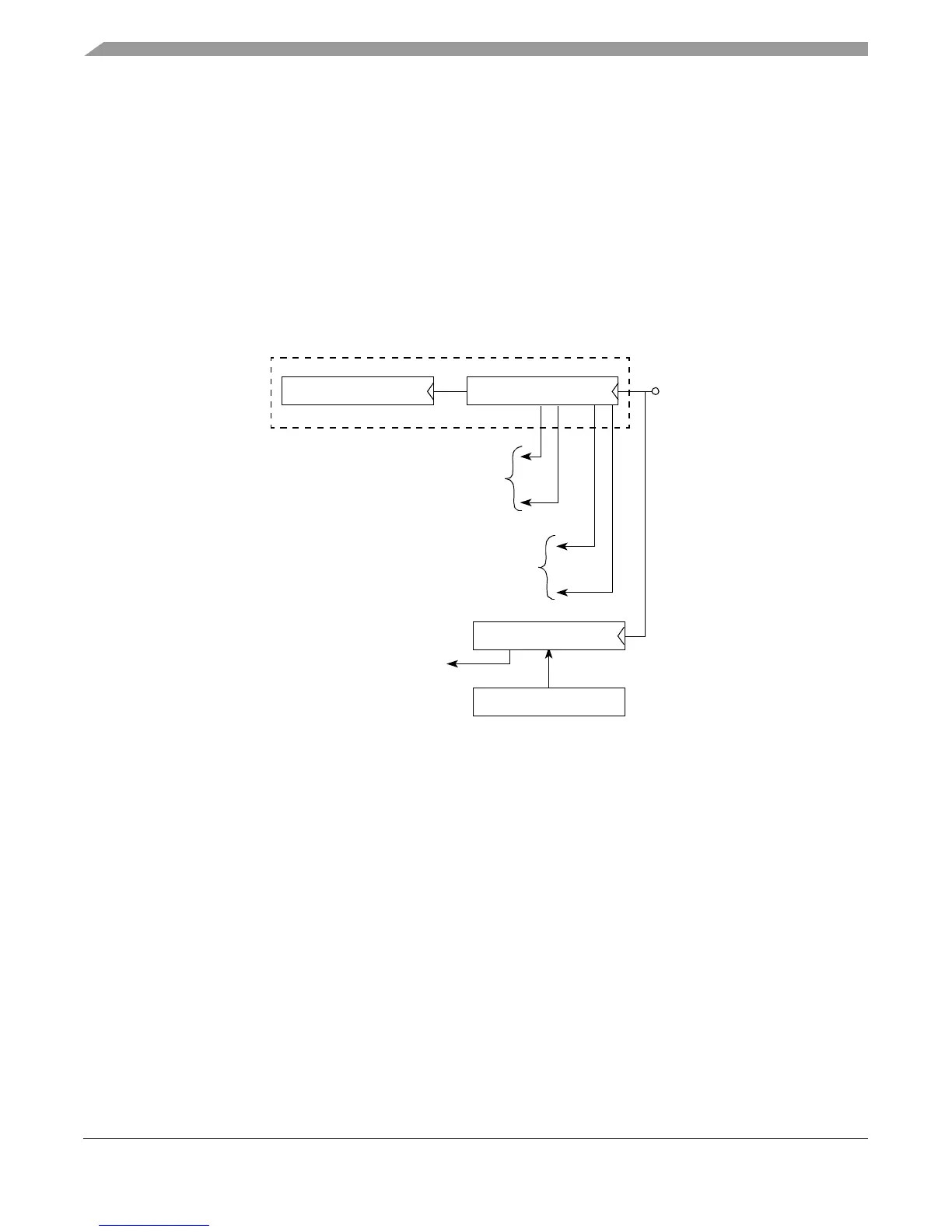

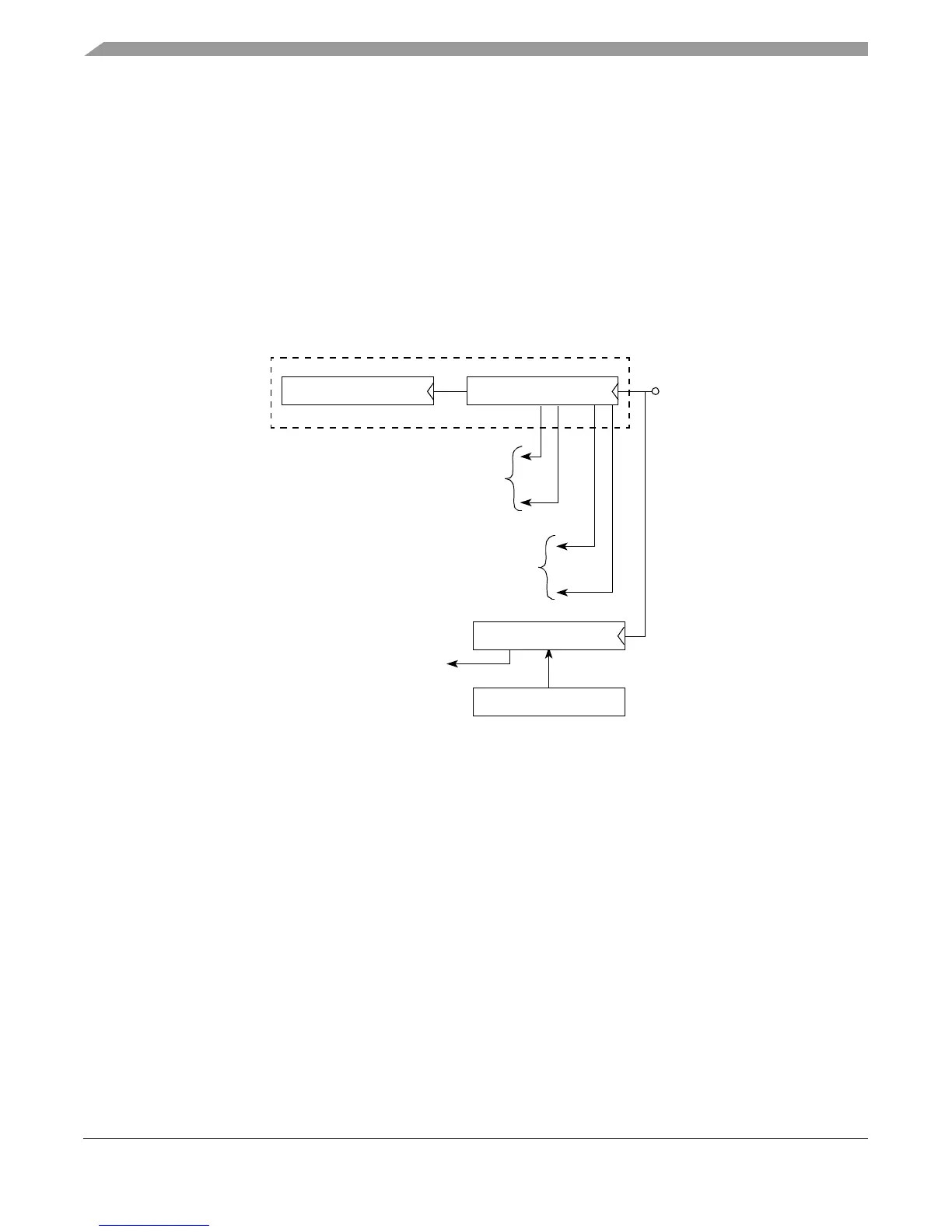

The relationship of these timer facilities to each other is shown in Figure 9-1.

Figure 9-1. Relationship of Timer Facilities to Time Base

9.2 Timer Registers

This section describes registers used by the timer facilities.

• HID0—Clock source select and enable: The clock source for the core timer facilities is

specified by two fields in the hardware implementation-dependent register 0 (HID0): time

base enable (TBEN), and select time base clock (SEL_TBCLK). HID0[TBEN] enables the

time base, and HID0[SEL_TBCLK] selects the time base clock, tbclk. (Some

implementations may use a signal with a different name.) For more information, see

Section 2.10.1, “Hardware Implementation-Dependent Register 0 (HID0).” Section 9.3,

“The e500 Timer Implementation,” describes how these bits interact with other registers.

• Timer control register (TCR). Provides control information for the on-chip timer of the core

complex. The core complex implements two fields not specified in Book E: TCR[WPEXT]

Timer Clock

Decrementer event = 0/1 detect

63

DECAR

32

Auto-reload

6332

TBL

6332

TBU

(Decrementer)

Watchdog timer events based on one of the TB bits

selected by the EIS-defined TCR[WPEXT] concatenated

with the Book E–defined TCR[WP] (WPEXT||WP).

Fixed-interval timer events based on one of TB bits selected

by the EIS-defined TCR[FPEXT] concatenated with the Book

E–defined TCR[FP] (FPEXT||FP).

DEC

•

•

•

•

•

•

(Time Base Clock)

tbclk

Loading...

Loading...