Register Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 2-37

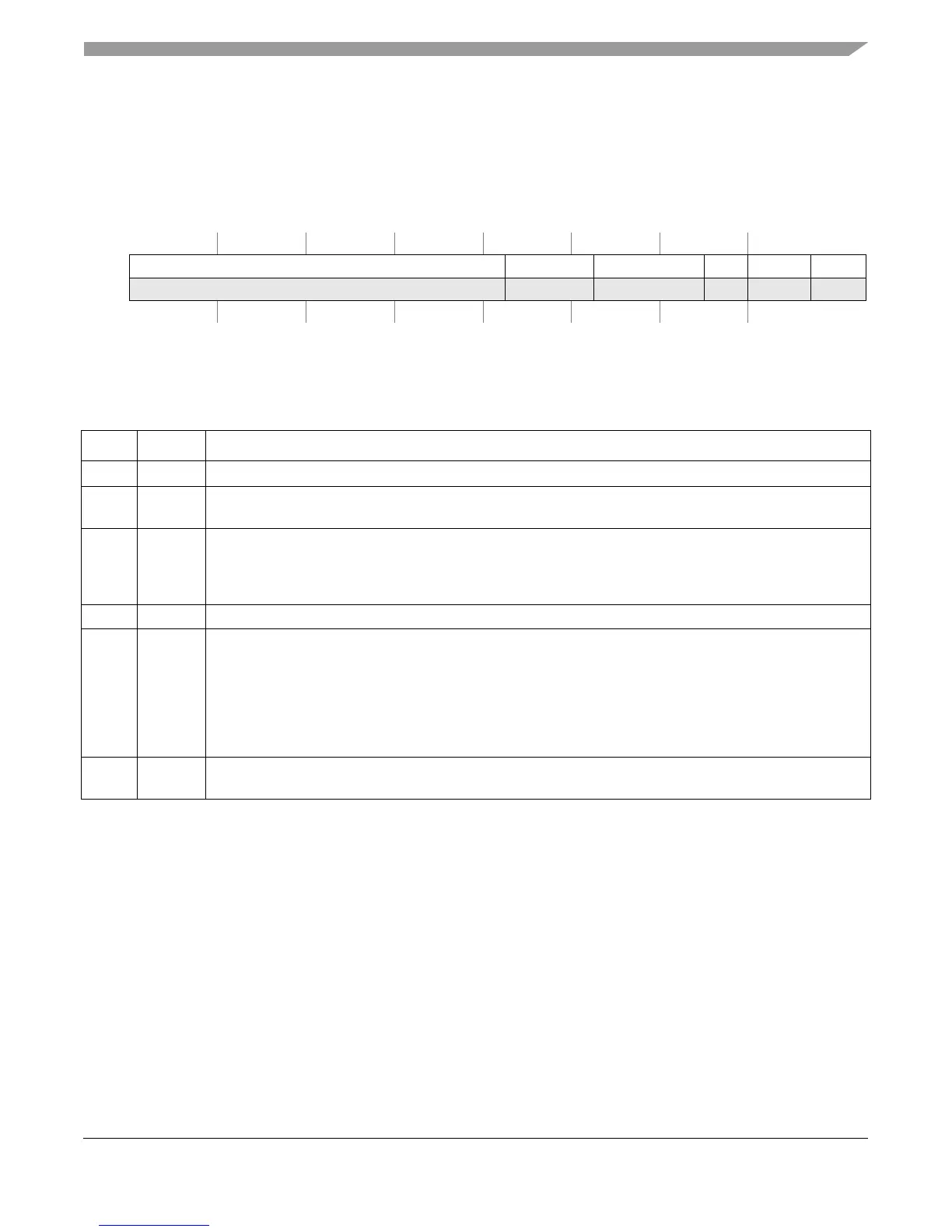

2.12.3 MMU Configuration Register (MMUCFG)

The MMUCFG register, shown in Figure 2-26, provides configuration information about the e500

MMU.

Table 2-21 describes the MMUCFG fields.

2.12.4 TLB Configuration Registers (TLB

n

CFG)

The TLBnCFG read-only registers provide information about each specific TLB that is visible to

the programming model.

SPR 1015 Access: Supervisor read-only

32 48 49 52 53 57 58 59 60 61 62 63

R— NPIDS PIDSIZE — NTLBS MAVN

W

Reset0000000000000000001100011100 0 1 0 0

Figure 2-26. MMU Configuration Register (MMUCFG)

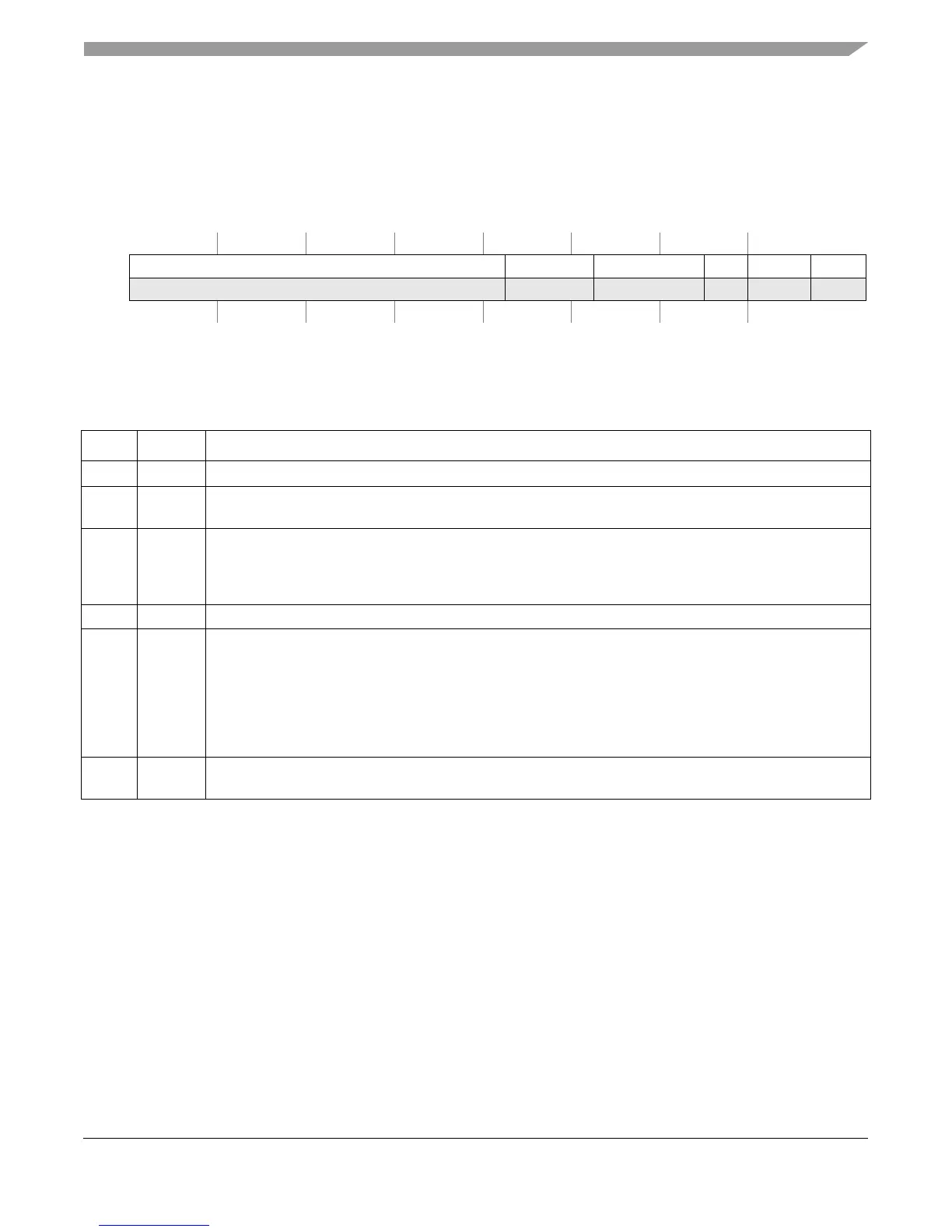

Table 2-21. MMUCFG Field Descriptions

Bits Name Description

32–48 — Reserved, should be cleared.

49–52 NPIDS Number of PID registers. A 4-bit field that indicates the number of PID registers provided by the processor.

The e500 implements three PIDs.

53–57 PIDSIZE PID register size. The 5-bit value of PIDSIZE is one less than the number of bits in each of the PID registers

implemented by the processor. The processor implements only the least significant PIDSIZE+1 bits in the

PID registers.

00111 Indicates 8-bit registers. This is the value presented by the e500.

58–59 — Reserved, should be cleared.

60–61 NTLBS Number of TLBs. The value of NTLBS is one less than the number of software-accessible TLB structures

that are implemented by the processor. NTLBS is set to one less than the number of TLB structures so that

its value matches the maximum value of MAS0[TLBSEL].)

00 1 TLB

01 2 TLBs. This is the value presented by the e500.

10 3 TLBs

11 4 TLBs

62–63 MAVN MMU architecture version number. Indicates the version number of the architecture of the MMU implemented

by the processor. 0b00 indicates version 1.0.

Loading...

Loading...