Register Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 2-39

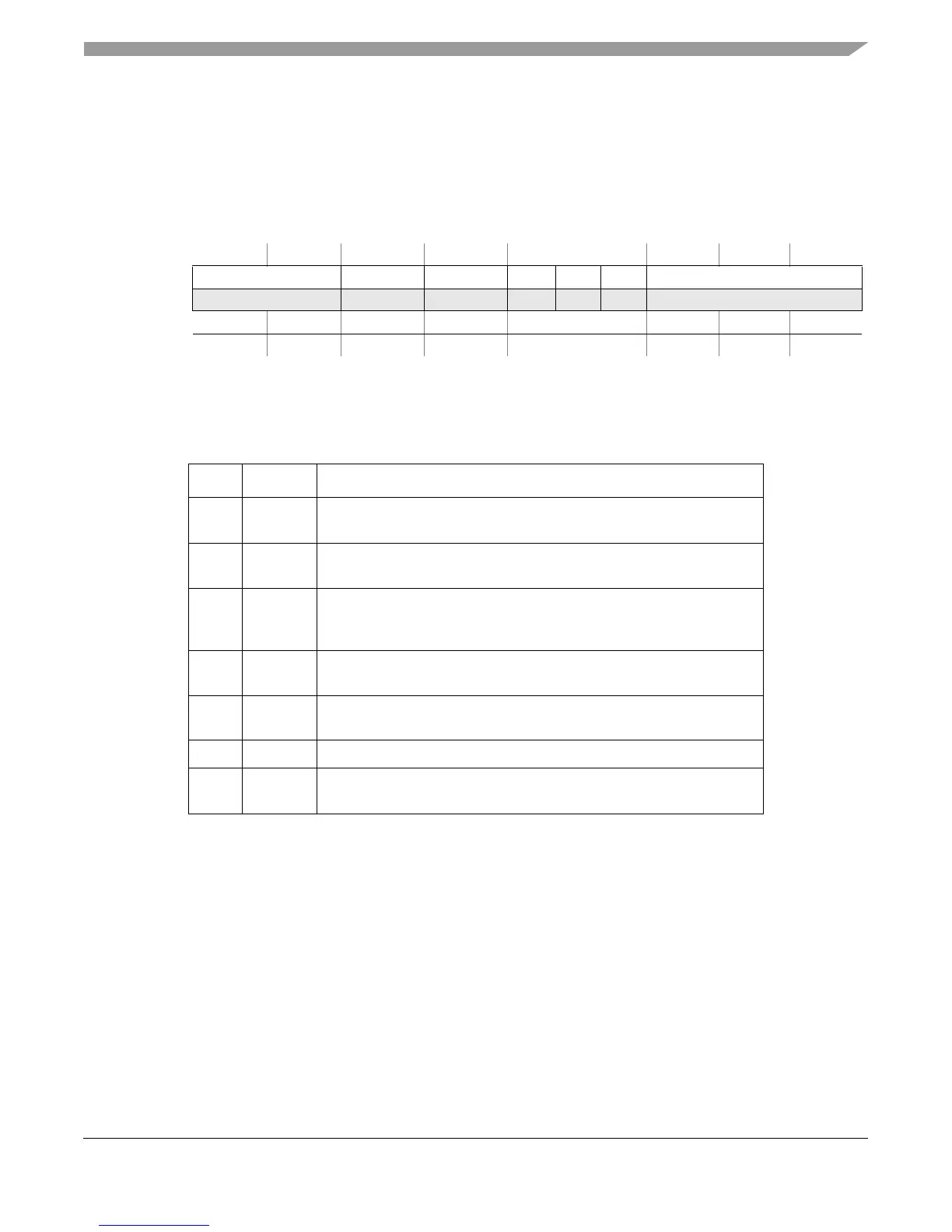

2.12.4.2 TLB1 Configuration Register 1 (TLB1CFG)

The TLB1CFG register, shown in Figure 2-28, provides configuration information for TLB1 of

the L2 MMU supplied with this version of the e500 core complex.

Table 2-23 describes the TLB1CFG fields.

2.12.5 MMU Assist Registers (MAS0–MAS4, MAS6–MAS7)

MMU assist registers, MASn are implementation-defined SPRs used by the MMU to manage

pages and TLBs. They, along with MAS5 (which is not implemented in the e500), are defined by

the Freescale implementation standard. Note that some fields in these registers are redefined on

the e500.

SPR 689 Access: Supervisor read-only

32 39 40 43 44 47 48 49 50 51 52 63

R ASSOC MINSIZE MAXSIZE IPROT AVAIL — NENTRY

W

Reset(e500v1)00010000 0 0 0 1 1 0 0 1 1 1 0 0 000000010000

Reset (e500v2)00010000 0 0 0 1 1 0 1 1 1 1 0 0 000000010000

Figure 2-28. TLB Configuration Register 1 (TLB1CFG)

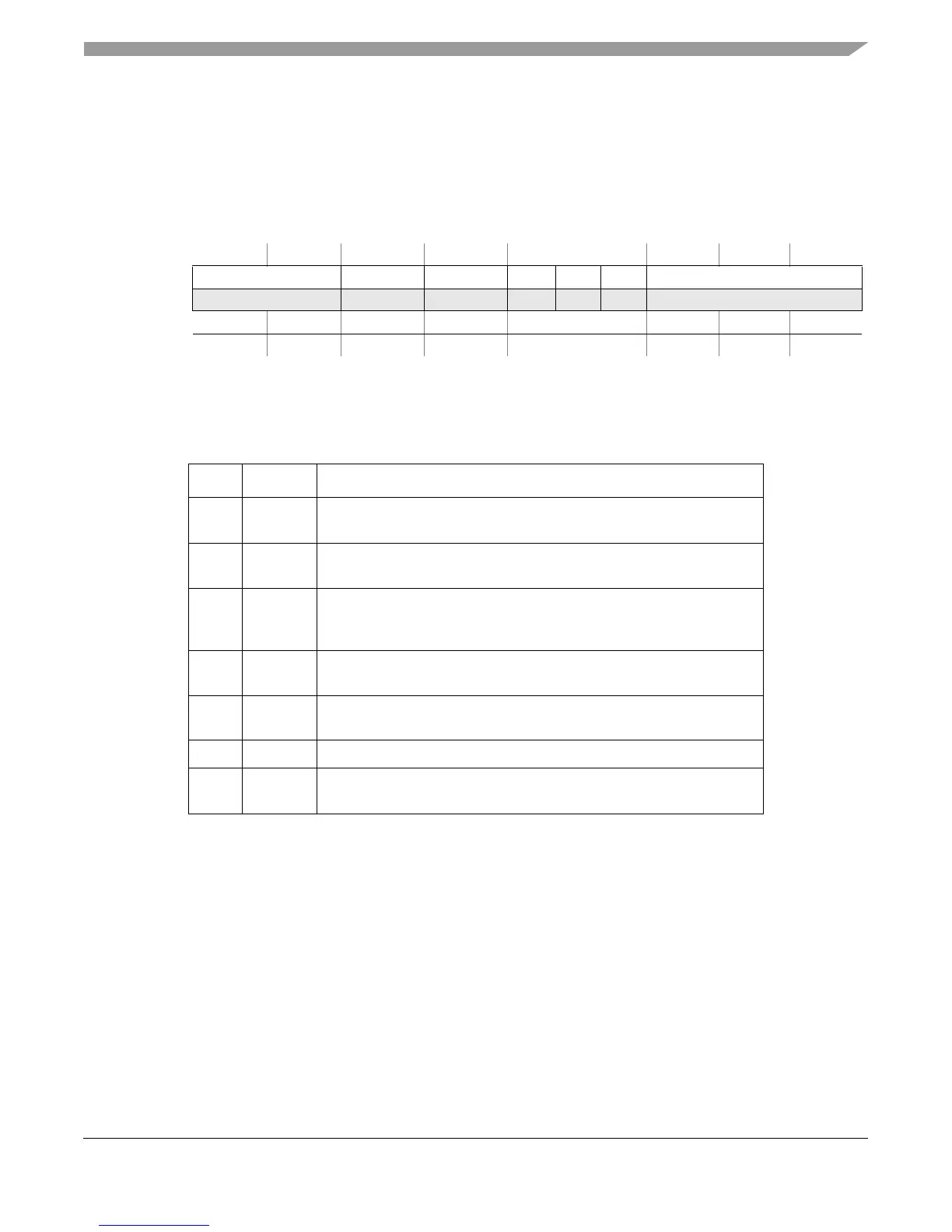

Table 2-23. TLB1CFG Field Descriptions

Bits Name Description

32–39 ASSOC Associativity of TLB1

0x10 Indicates associativity is 16

40–43 MINSIZE Minimum page size of TLB1

0x1 Indicates smallest page size is 4 Kbytes

44–47 MAXSIZE Maximum page size of TLB1

0x9 Indicates maximum page size is 256 Mbytes (e500v1)

0xB Indicates maximum page size is 4 Gbytes (e500v2)

48 IPROT Invalidate protect capability of TLB1

1 Indicates that TLB1 supports invalidate protection capability

49 AVAIL Page size availability of TLB1

1 Indicates all page sizes between MINSIZE and MAXSIZE supported

50–51 — Reserved, should be cleared.

52–63 NENTRY Number of entries in TLB1

0x010 TLB1 contains 16 entries

Loading...

Loading...