PowerPC e500 Core Family Reference Manual, Rev. 1

3-52 Freescale Semiconductor

Instruction Model

3.8.1.2 SPE Integer and Fractional Operations

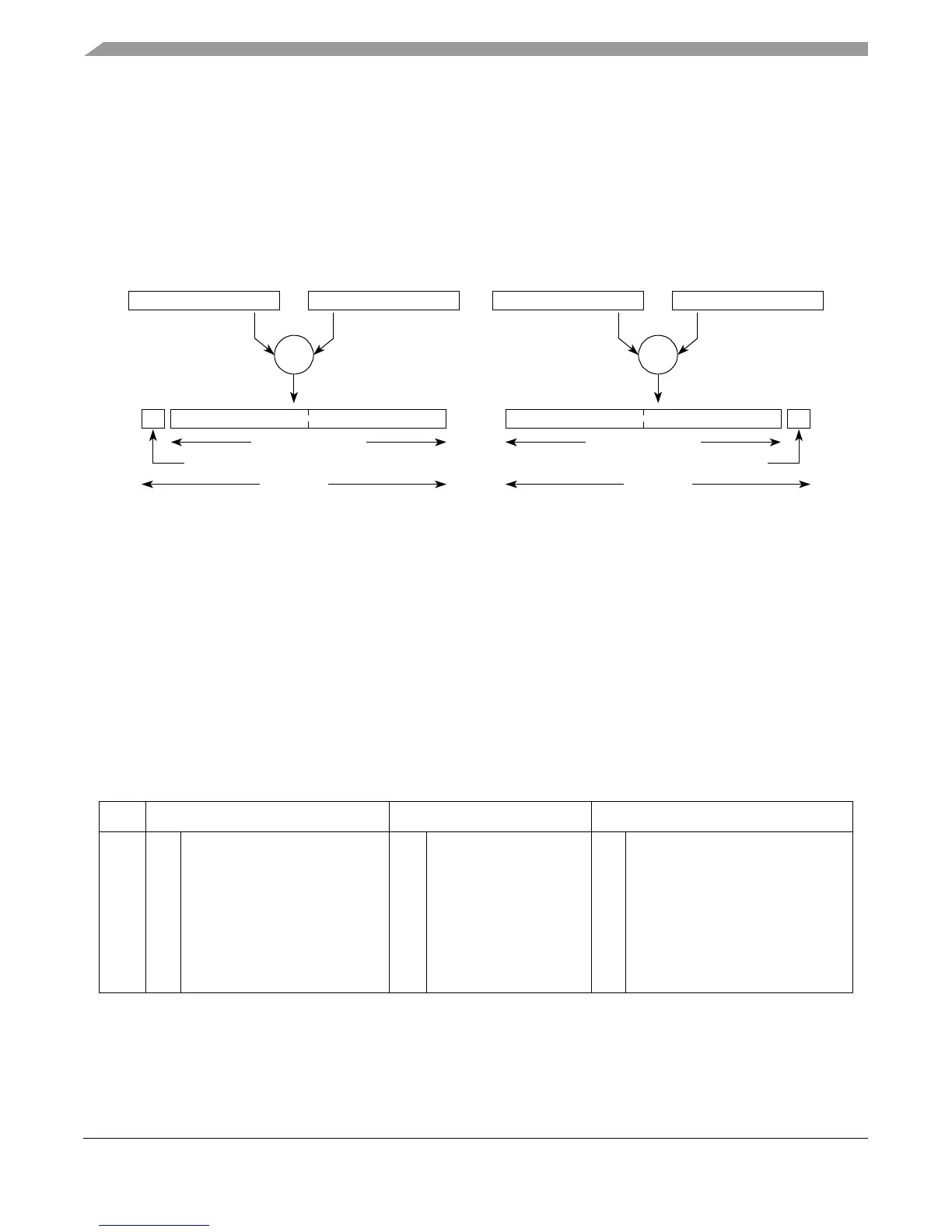

Figure 3-5 shows data formats for signed integer and fractional multiplication. Note that low word

versions of signed saturate and signed modulo fractional instructions are not supported.

Attempting to execute an opcode corresponding to these instructions causes boundedly undefined

results.

Figure 3-5. Integer and Fractional Operations

3.8.1.3 SPE APU Instructions

SPE APU instructions treat 64-bit GPRs as being composed of a vector of two 32-bit elements.

(Some instructions also read or write 16-bit elements.) The SPE APU supports a number of forms

of multiply and multiply-accumulate operations, and of add and subtract to accumulator

operations. The SPE supports signed and unsigned forms, and optional fractional forms. For these

instructions, the fractional form does not apply to unsigned forms because integer and fractional

forms are identical for unsigned operands.

Table 3-34 shows how SPE APU vector multiply instruction mnemonics are structured.

Table 3-34. SPE APU Vector Multiply Instruction Mnemonic Structure

Prefix Multiply Element Data Type Element Accumulate Element

evm

ho

he

hog

heg

wh

wl

whg

wlg

w

half odd (16x16→32)

half even (16x16→32)

half odd guarded (16x16→32)

half even guarded (16x16→32)

word high (32x32→32)

word low (32x32→32)

word high guarded (32x32→32)

word low guarded (32x32→32)

word (32x32→64)

usi

umi

ssi

ssf

1

smi

smf

1

1

Low word versions of signed saturate and signed modulo fractional instructions are not supported. Attempting to execute

an opcode corresponding to these instructions causes boundedly undefined results.

unsigned saturate integer

unsigned modulo integer

signed saturate integer

signed saturate fractional

signed modulo integer

signed modulo fractional

a

aa

an

aaw

anw

write to ACC

write to ACC & added ACC

write to ACC & negate ACC

write to ACC & ACC in words

write to ACC & negate ACC in words

S S

×

S SHP LP

2N Bits

(2N–1)–Bit Product

Signed Multiplier

Sign Extension

S S

×

0SHP LP

2N Bits

(2N–1)–Bit Product

Signed Multiplier

Zero fill

Integer Fractional

Signed Multiplication N

× N → 2N – 1 Bits

Loading...

Loading...