PowerPC e500 Core Family Reference Manual, Rev. 1

3-50 Freescale Semiconductor

Instruction Model

There is no record form of SPE or embedded floating-point instructions. Vector compare

instructions store the result of the comparison into the CR. The meaning of the CR bits is now

overloaded for vector operations. Vector compare instructions specify a CR field and two source

registers as well as the type of compare: greater than, less than, or equal. Two bits in the CR field

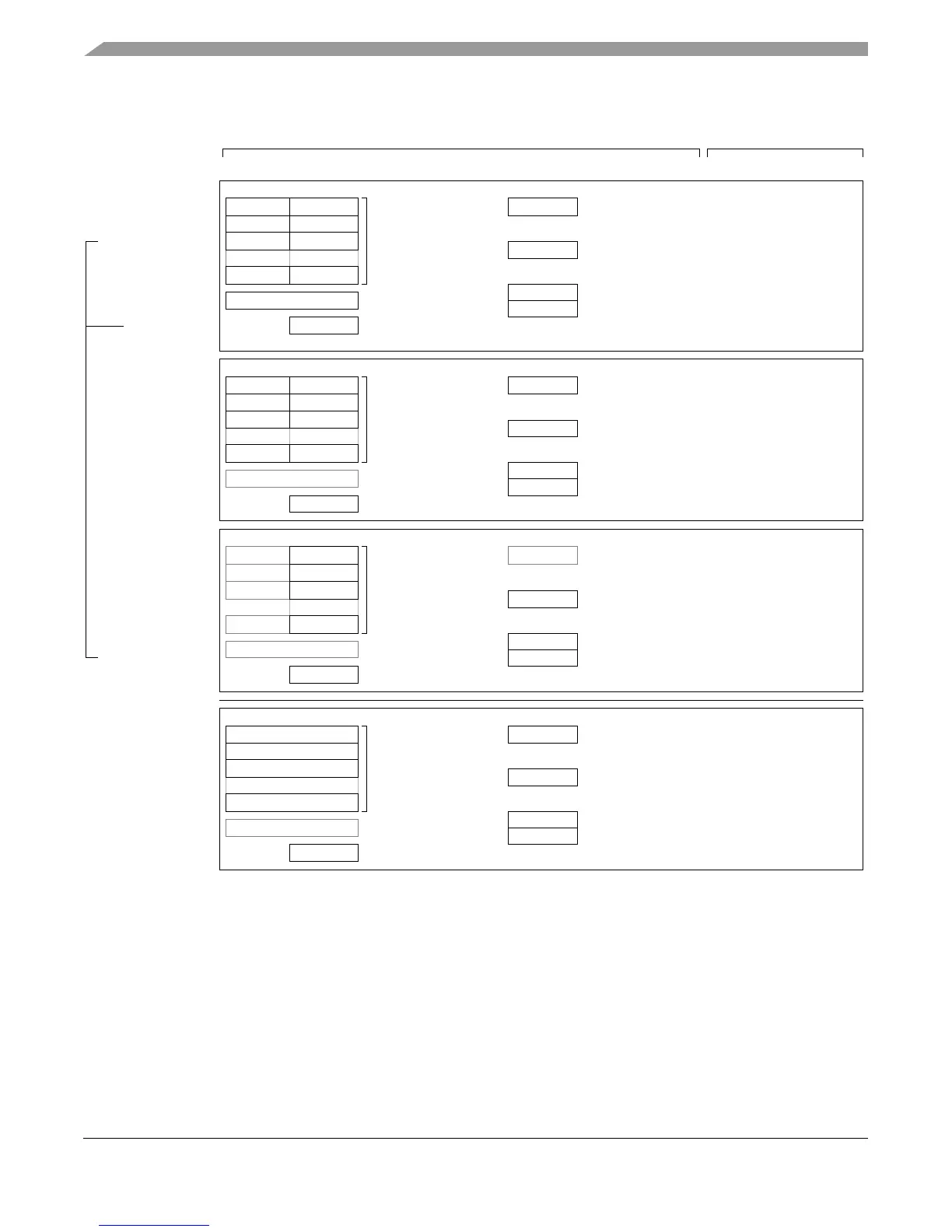

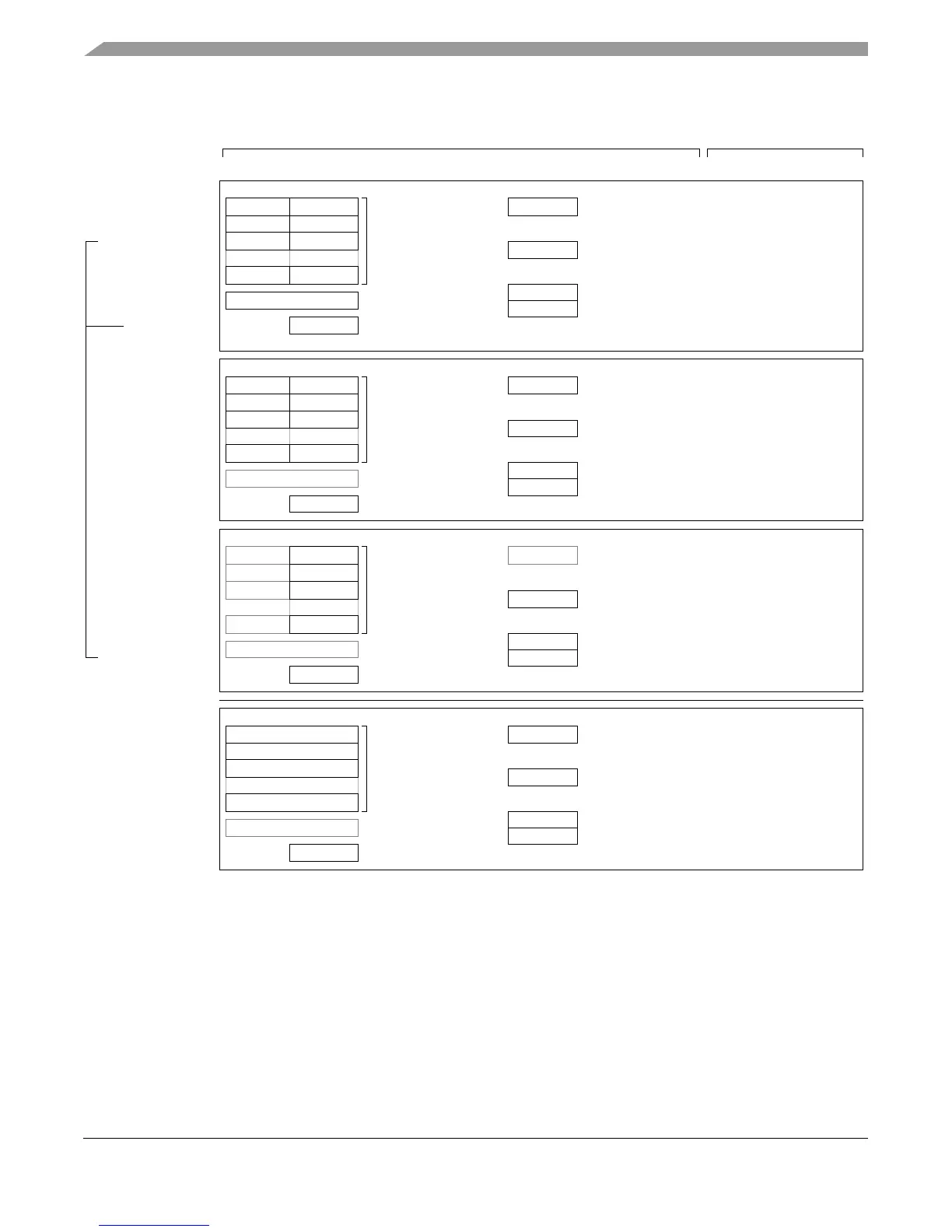

Register Model Instruction Model

User-Level Registers Supervisor-Level Registers

Computation Load/Store

0 31 32 63 32 63

brinc

evmra

evm…

evabs

evadd…

evand…

evfsctuiz

evcntl…

evdiv…

evmerge…

evsub…

logical, rotate,

shift, extend,

round, select,

compare

evldh…

evldw…

evldd…

evl…splat…

evlwhos…

evlwh…

evstdd…

evstdh…

evstdw…

evstwh…

Int/Frac Int/Frac

General-purpose

registers (GPRs)

MSR[SPE] Machine state

Int/Frac Int/Frac

Interrupt Registers

Int/Frac Int/Frac

spr 62 ESR[SPE] Exception syndrome

SPE APU

……

Int/Frac Int/Frac

Interrupt Vector Offset Registers

spr 405 IVOR5 Alignment

ACC Accumulator

spr 528 IVOR32 SPE/Embedded

Floating-point

Original SPE

APU

SPE/floating-point

status/control

spr 512 SPEFSCR

Vector

Single-Precision

Floating-Point

APU

0 31 32 63 32 63

efvcf…

efvct…

efvabs

efvadd

efvcmp…

efvdiv

efvmul

efvneg

efvnabs

efvsub

efvtst…

From SPE:

evmergehi

evmergelo

From SPE:

evldd

evlddx

evstdd

evstddx

Single-prec. Single-prec.

General-purpose

registers (GPRs)

1

MSR[SPE] Machine state

Single-prec. Single-prec.

Interrupt Registers

Single-prec. Single-prec.

spr 62 ESR[SPE] Exception syndrome

……

Single-prec. Single-prec.

Interrupt Vector Offset Registers

spr 405

IVOR5

Alignment

ACC Accumulator

spr 528

IVOR32 SPE/Embedded

Floating-point

SPE/floating-point

status/control

spr 512 SPEFSCR

Scalar

Single-Precision

Floating-Point

APU

0 31 32 63 32 63 efscf…

efsct…

efsabs

efsadd

efscmp…

efsdiv

efsmul

efsneg

efsnabs

efssub

efstst…

Uses

PowerPC

UISA 32-bit

loads and

stores

Single-prec.

General-purpose

registers (GPRs)

1

MSR[SPE]

Machine state

(e500v1 only)

Single-prec.

Interrupt Registers

Single-prec.

spr 62 ESR[SPE] Exception syndrome

…

Single-prec.

Interrupt Vector Offset Registers

spr 405

IVOR5

Alignment

ACC Accumulator

spr 528

IVOR32 SPE/Embedded

Floating-point

SPE/floating-point

status/control

spr 512 SPEFSCR

Scalar

Double-Precision

Floating-Point

APU

(e500v2 only)

0 31 32 63 32 63 efdcf…

efdct…

efdabs

efdadd

efdcmp…

efddiv

efdmul

efdneg

efdnabs

efdsub

efdtst…

From SPE:

evmergehi

evmergelo

From SPE:

evldd

evlddx

evstdd

evstddx

Double-precision

General-purpose

registers (GPRs)

1

MSR[SPE] Machine state

Double-precision

Interrupt Registers

Double-precision

spr 62 ESR[SPE] Exception syndrome

…

Double-precision

Interrupt Vector Offset Registers

spr 405

IVOR5

Alignment

ACC Accumulator

spr 528

IVOR32 SPE/Embedded

Floating-point

SPE/floating-point

status/control

spr 512 SPEFSCR

Note: Gray text indicates that APU does not use this register or register field.

1

Formatting of floating-point operands is as defined by IEEE 754, as described in the APU chapter of the EREF.

Figure 3-4. SPE and Floating-Point APU GPR Usage

Loading...

Loading...