PowerPC e500 Core Family Reference Manual, Rev. 1

2-48 Freescale Semiconductor

Register Model

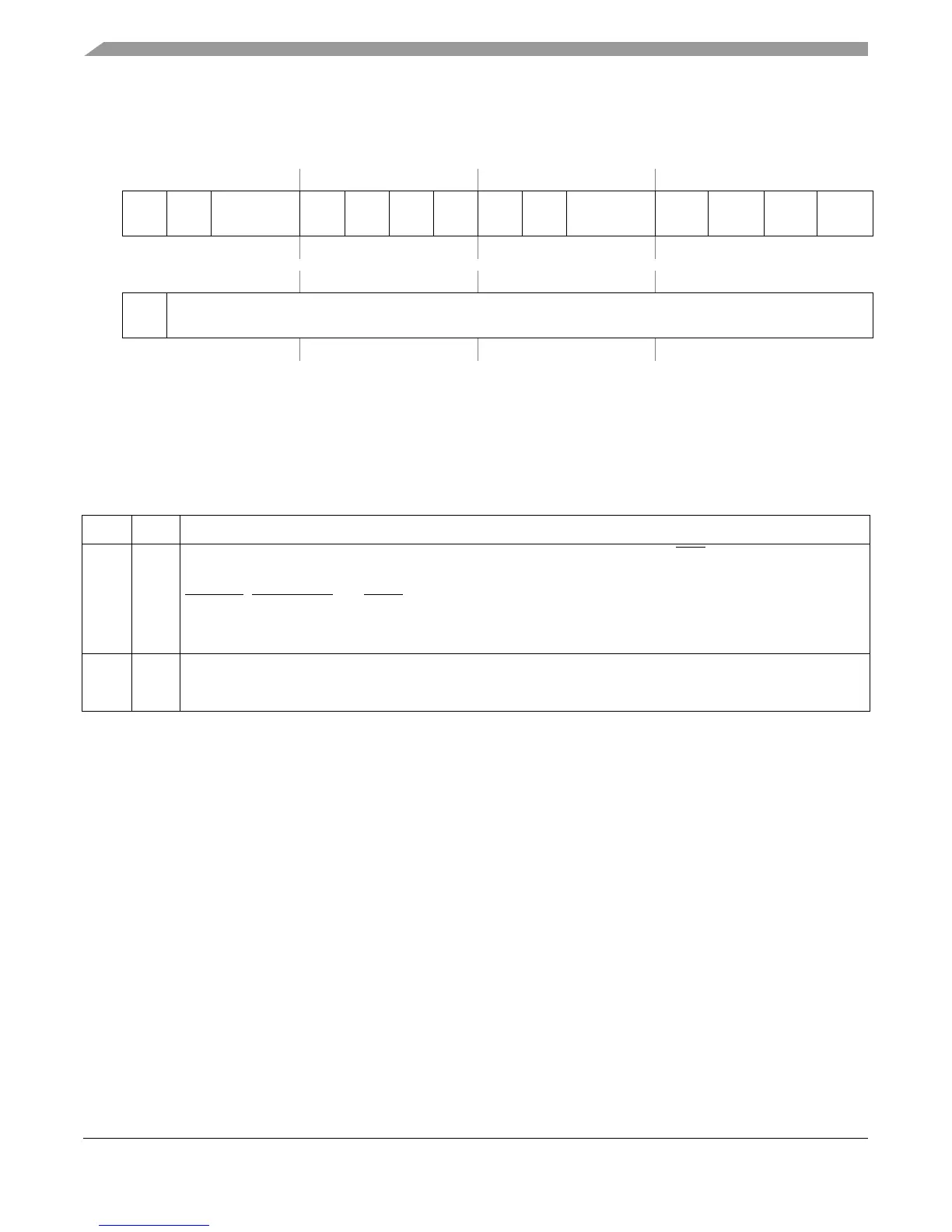

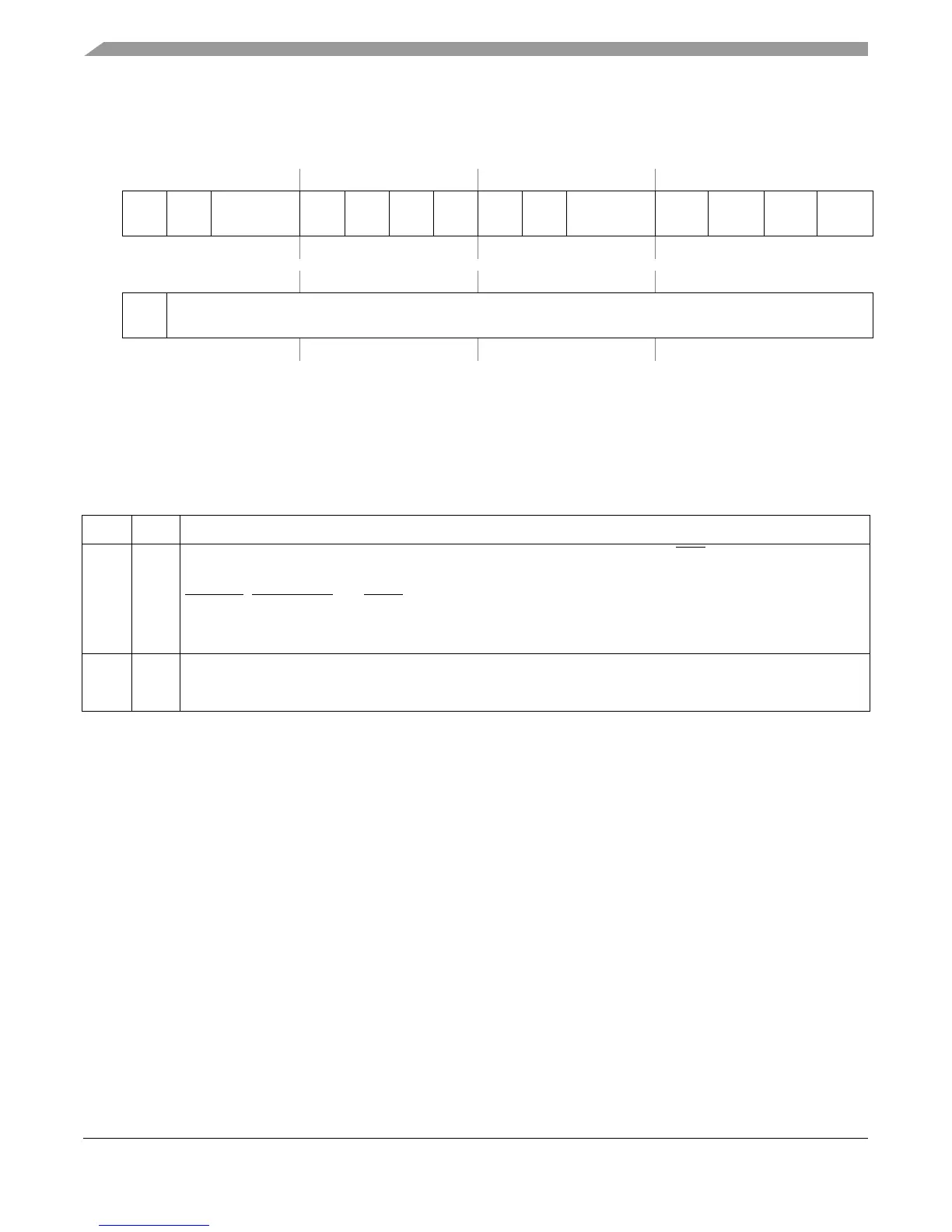

DBSR is shown in Figure 2-37.

The DBSR is set through hardware but is read and cleared through software. DBSR is read using

mfspr. DBSR bits are cleared by writing ones to them; writing zeros has no effect. Table 2-34

describes DBSR field definitions.

2.13.3 Instruction Address Compare Registers (IAC1–IAC4)

The e500 implements the IAC1 and IAC2 as they are defined by the Book E architecture; it does

not implement IAC3 and IAC4.

A debug event may be enabled to occur upon an attempt to execute an instruction from an address

specified in an IAC, inside or outside a range specified by IAC1 and IAC2, or to blocks of

addresses specified by the combination of the IAC1 and IAC2. Because all instruction addresses

are required to be word-aligned, the two low-order bits of the IACs are reserved and do not

participate in the comparison to the instruction address.

2.13.4 Data Address Compare Registers (DAC1–DAC2)

The e500 implements the DAC1 and DAC2 as they are defined by the Book E architecture. A

debug event may be enabled to occur upon loads, stores, or cache operations to an address

specified in either DAC1 or DAC2, inside or outside a range specified by the DAC1 and DAC2,

SPR: 304 Access: Supervisor-only

32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47

R

IDE UDE MRR ICMP BRT IRPT TRAP IAC1 IAC2 — DAC1R DAC1W DAC2R DAC2W

W

Reset 0 0 undefined 00000000 0 0 0 0

48 49 63

R

RET —

W

Reset000000000000 0 0 0 0

Figure 2-37. Debug Status Register (DBSR)

Table 2-34. DBSR Implementation-Specific Field Descriptions

Bits Name Description

33 UDE Unconditional debug event. Set if an unconditional debug event occurred. If the UDE

signal (level sensitive,

active low) is asserted, DBSR[UDE] is affected as follows:

MSR[DE]

DBCR0[IDM] Action

X 0 No action.

0 1 DBSR[UDE] is set.

1 1 DBSR[UDE] is set and a debug interrupt is taken.

34–35 MRR Most recent reset. Set when a reset occurs. Undefined at power-up. The e500 implements HRESET as follows:

0x No hard reset occurred since this bit was last cleared by software.

1x The previous reset was a hard reset.

Loading...

Loading...