PowerPC e500 Core Family Reference Manual, Rev. 1

3-24 Freescale Semiconductor

Instruction Model

The branch always encoding of the BO operand does not have a y bit.

The 5-bit BI operand in branch conditional instructions specifies which CR bit represents the

condition to test. The CR bit selected is BI +32

If the branch instructions contain immediate addressing operands, the target addresses can be

computed sufficiently ahead of the branch instruction that instructions can be fetched along the

target path. If the branch instructions use the link and count registers, instructions along the target

path can be fetched if the link or count register is loaded sufficiently ahead of the branch

instruction.

Branching can be conditional or unconditional, and optionally a branch return address is created by

storing the effective address of the instruction following the branch instruction in the LR after the

branch target address has been computed. This is done regardless of whether the branch is taken.

3.3.1.3.2 Branch Instructions

Table 3-17 lists branch instructions provided by the Book E processors. A set of simplified

mnemonics and symbols is provided for the most frequently used forms of branch conditional,

compare, trap, rotate and shift, and certain other instructions; see Appendix C, “Simplified

Mnemonics for PowerPC Instructions.” Note that the e500 does not use the BO operand for static

branch prediction.

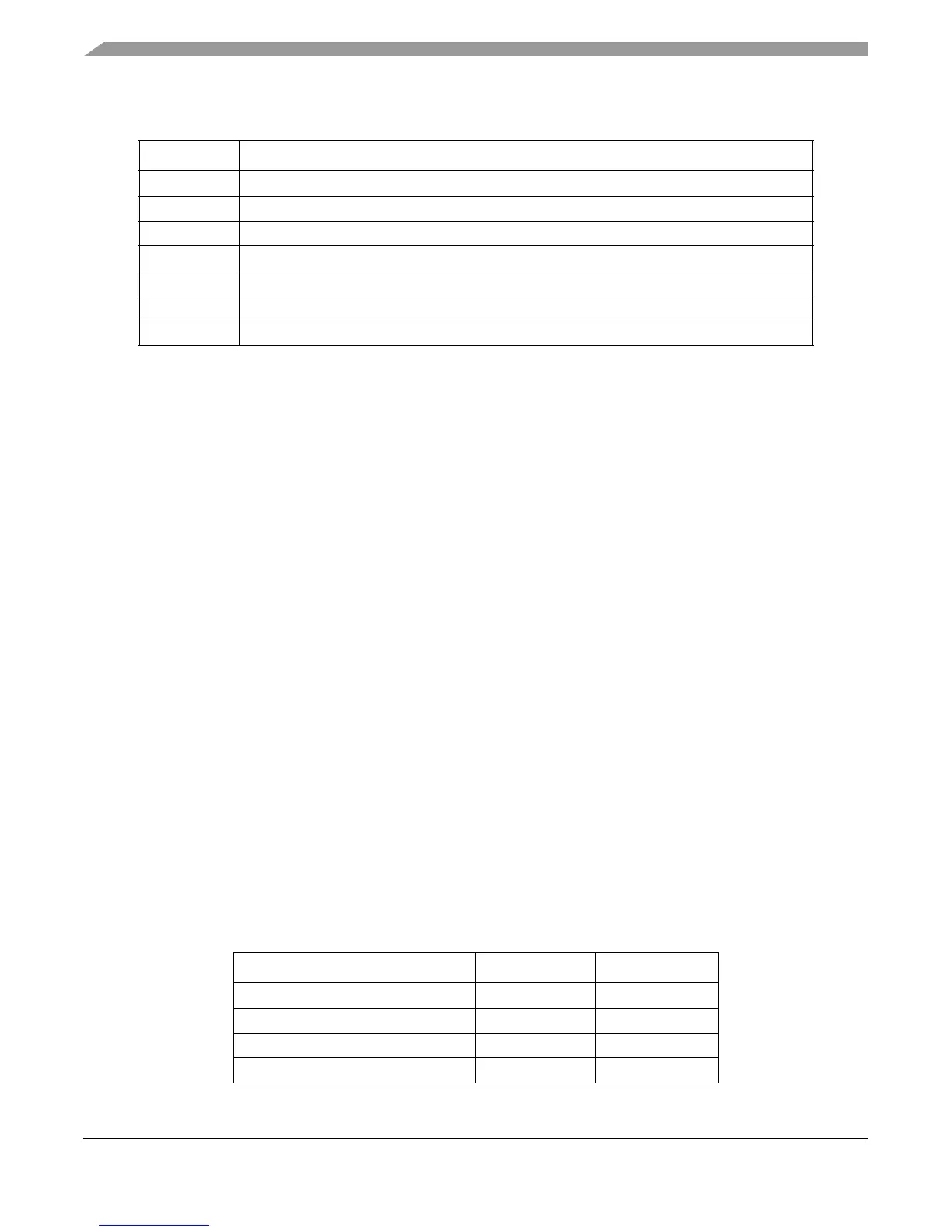

001

zy

Branch if the condition is FALSE.

0100

y

Decrement the CTR, then branch if the decremented CTR ≠ 0 and the condition is TRUE.

0101

y

Decrement the CTR, then branch if the decremented CTR = 0 and the condition is TRUE.

011

zy

Branch if the condition is TRUE.

1

z

00

y

Decrement the CTR, then branch if the decremented CTR ≠ 0.

1

z

01

y

Decrement the CTR, then branch if the decremented CTR = 0.

1

z

1

zz

Branch always.

In this table,

z

indicates a bit that is ignored. Note that the

z

bits should be cleared, as they may be assigned

a meaning in some future version of the architecture.

The

y

bit provides a hint about whether a conditional branch is likely to be taken and may be used by some

implementations to improve performance.

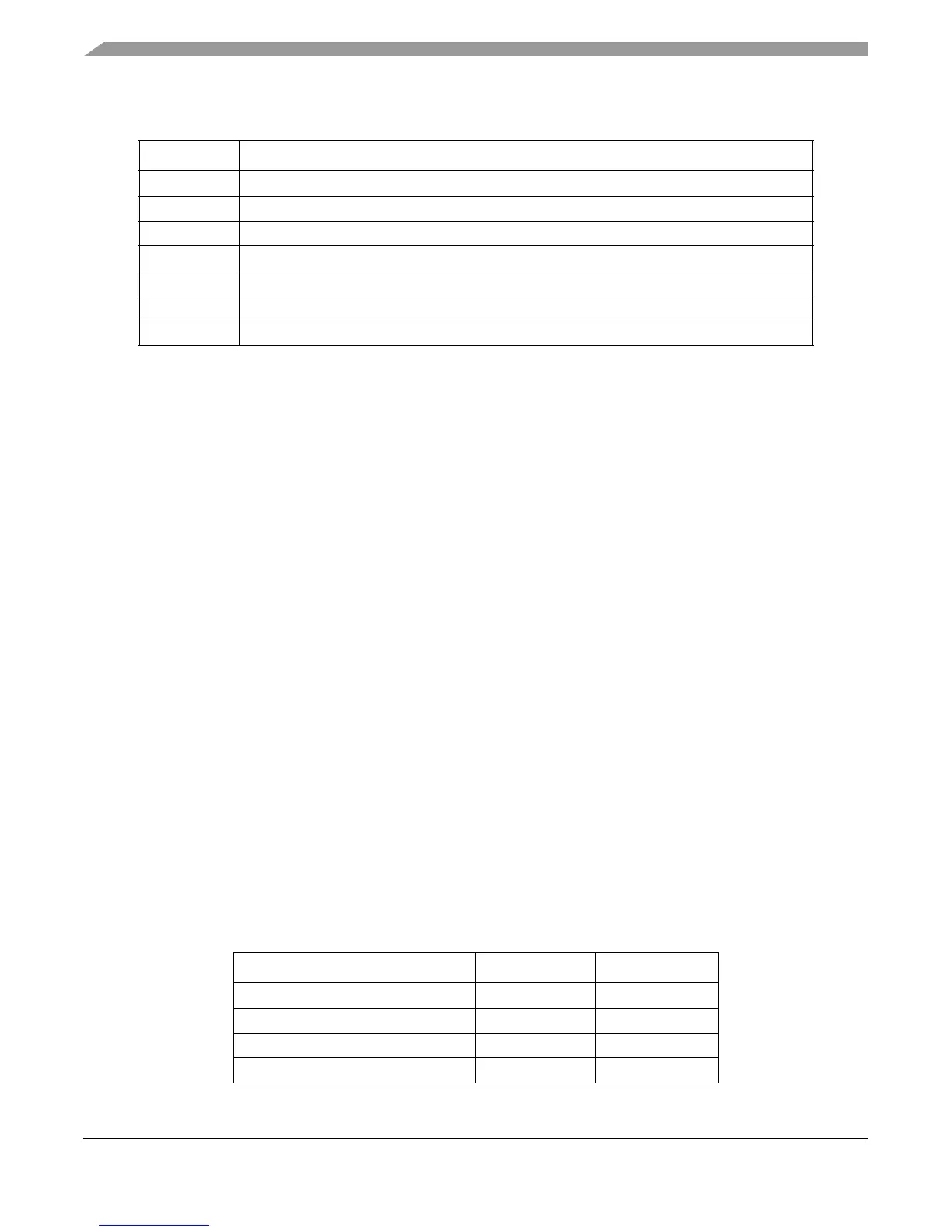

Table 3-17. Branch Instructions

Name Mnemonic Syntax

Branch b (ba bl bla) target_addr

Branch Conditional bc (bca bcl bcla) BO,BI,target_addr

Branch Conditional to Link Register bclr (bclrl) BO,BI

Branch Conditional to Count Register bcctr (bcctrl) BO,BI

Table 3-16. BO Operand Encodings (continued)

BO Description

Loading...

Loading...