PowerPC e500 Core Family Reference Manual, Rev. 1

5-24 Freescale Semiconductor

Interrupts and Exceptions

5.7.7 Program Interrupt

A program interrupt occurs when no higher priority exception exists and a program exception is

presented to the interrupt mechanism. A program interrupt is caused when any of the following

exceptions occurs during execution of an instruction.

SRR0, SRR1, MSR, and ESR are updated as shown in Table 5-18.

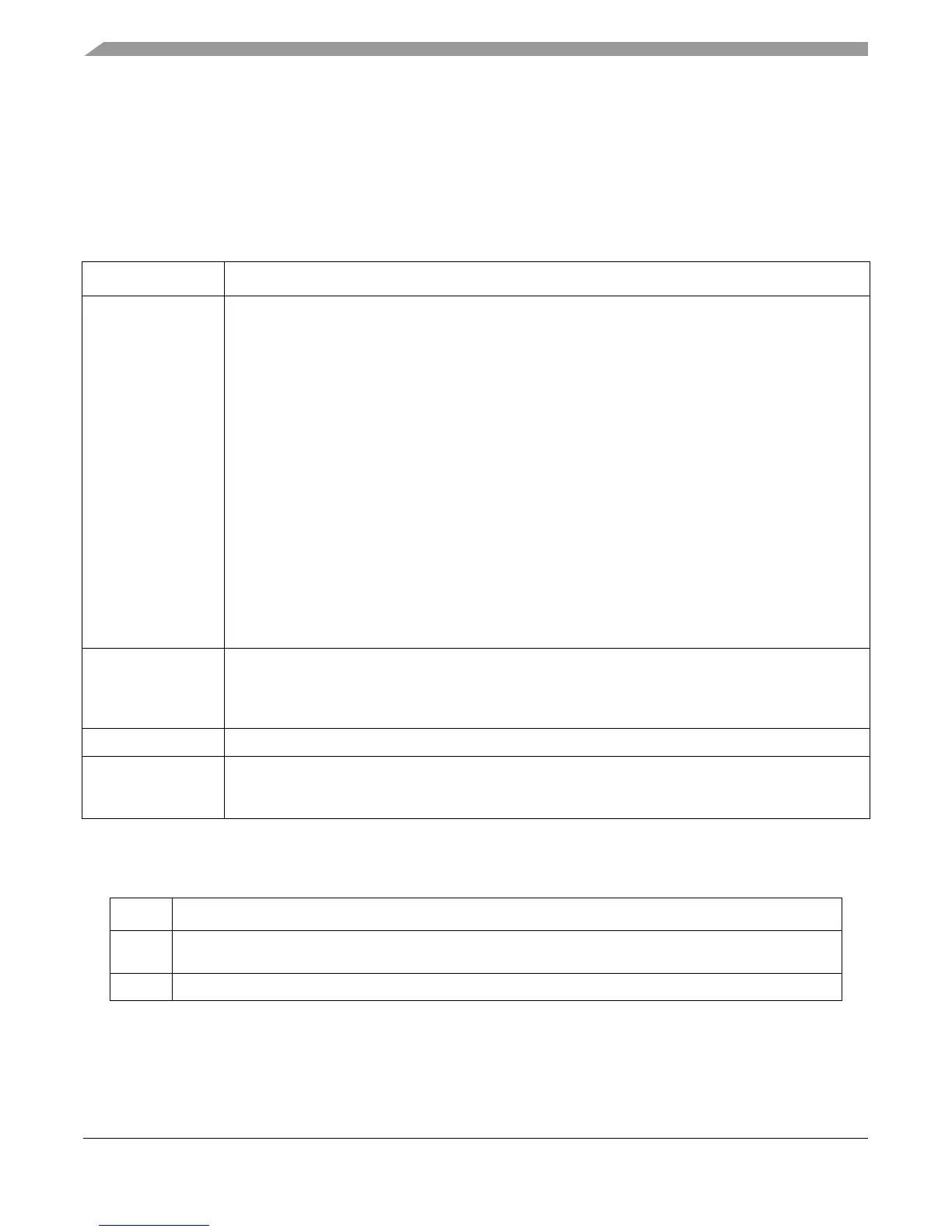

Table 5-17. Program Interrupt Exception Conditions

Exception Cause

Illegal instruction

exception

An illegal instruction exception always occurs when execution of any of the following kinds of instructions

is attempted.

• A reserved-illegal instruction

• In user mode, an mtspr or mfspr that specifies an SPRN value with SPRN[5] = 0 (user-mode

accessible) that represents an unimplemented SPR

• (EIS) If an invalid SPR address is accessible only in supervisor mode and the processor is in

supervisor mode (MSR[PR] = 0), results are undefined.

• (EIS) If the invalid SPR address is accessible only in the supervisor mode and the processor is in user

mode (MSR[PR] = 1), a privileged instruction exception is taken.

An illegal instruction exception may occur when execution is attempted of any of the following kinds of

instructions. If the exception does not occur, the alternative is shown in parentheses.

• An instruction that is in invalid form (boundedly undefined results). On the e500, all instructions have

invalid forms cause boundedly undefined results.

• A reserved no-op instruction (no-operation performed is preferred). There are no reserved no-ops for

the e500.

• A defined or allocated instruction that is not implemented (unimplemented operation exception).

Unimplemented Book E instructions such as mfapidi, mfdcr, and mtdcr take an illegal instruction

exception.

• The EIS defines that an attempt to execute a 64-bit Book E instruction causes an illegal instruction

exception.

Privileged instruction

exception

Occurs when MSR[PR] = 1 and execution is attempted of any of the following:

• A privileged instruction

•An mtspr or mfspr instruction that specifies a privileged SPR (SPRN[5] = 1)

• (EIS) An mtpmr or mfpmr instruction that specifies a privileged PMR (PMRN[5] = 1)

Trap exception A trap exception occurs when any of the conditions specified in a trap instruction are met.

Unimplemented

operation exception

An unimplemented operation exception may occur when a defined or allocated instruction is encountered

that is not implemented. Otherwise an illegal instruction exception occurs. On the e500, these instructions

are mfapidi, mfdcr, and mtdcr and they take an illegal instruction exception.

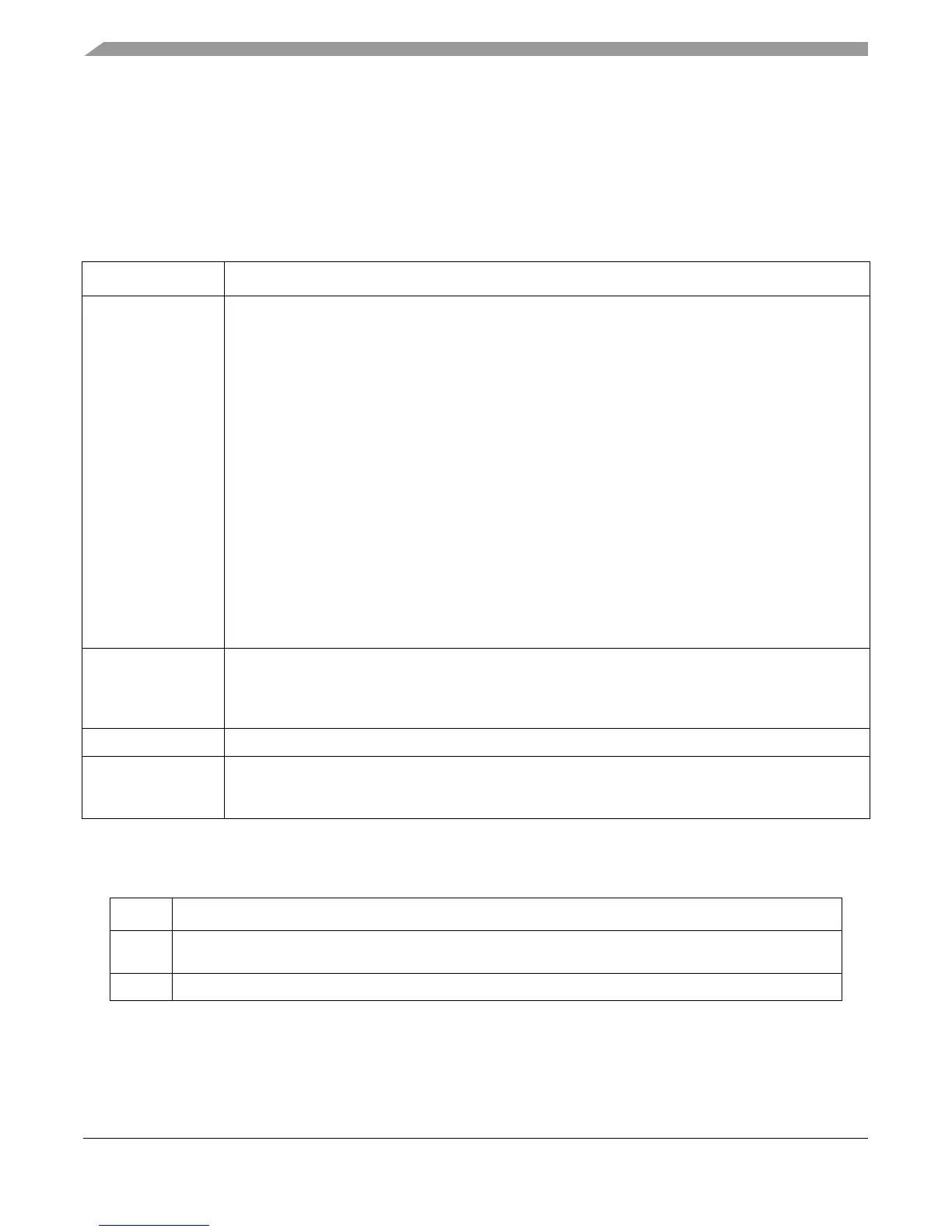

Table 5-18. Program Interrupt Register Settings

Register Description

SRR0 For all program interrupts except an enabled exception when in an imprecise mode (see Table 5 -19), set to

the EA of the instruction that caused the interrupt.

SRR1 Set to the MSR contents at the time of the interrupt.

Loading...

Loading...