Memory Management Units

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 12-31

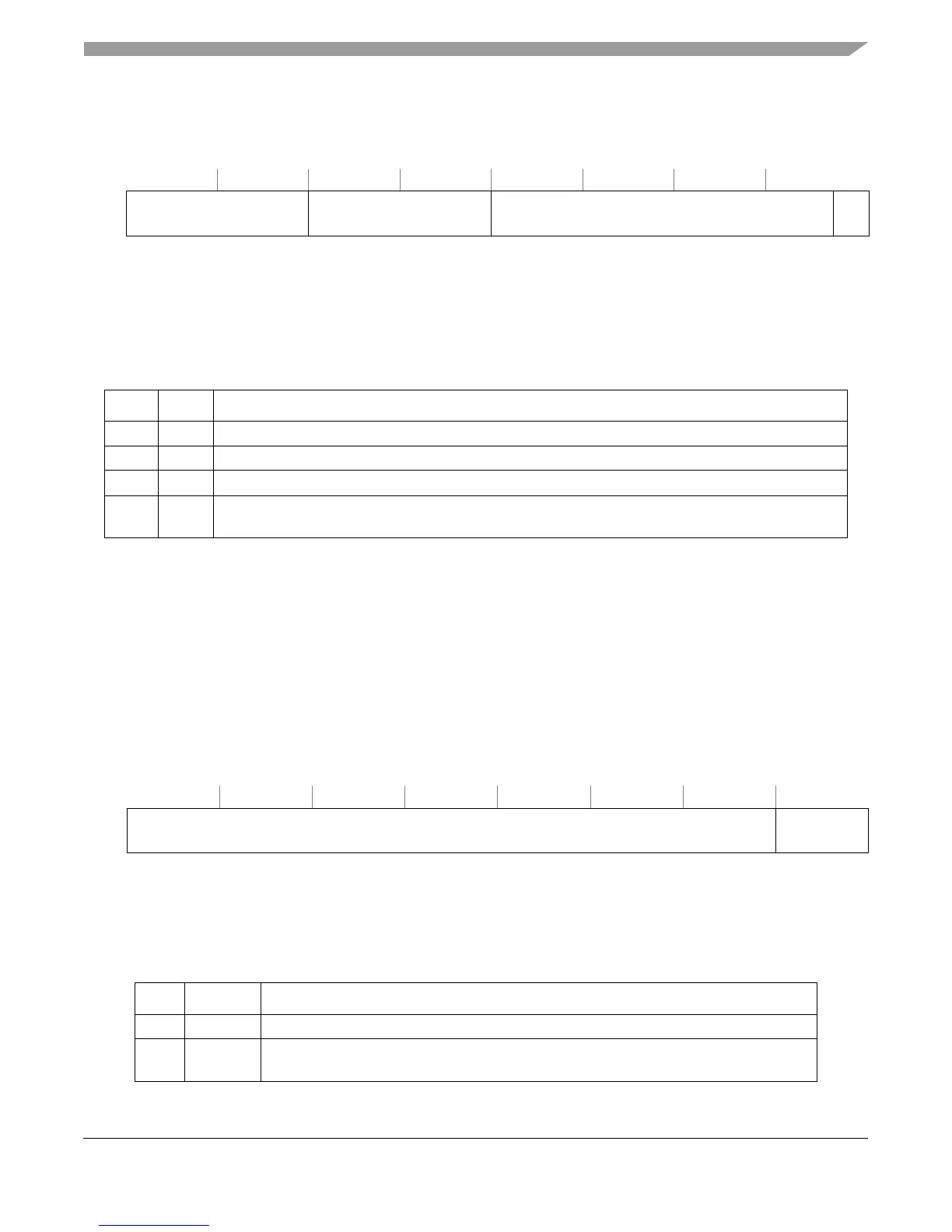

Figure 12-16 shows the format of MAS6.

Table 12-13 shows the core complex MAS6 bit definitions. Note that while the Freescale Book E

allows for a SPIDx field of 12 bits, SPID0 on the core complex is only an 8-bit field.

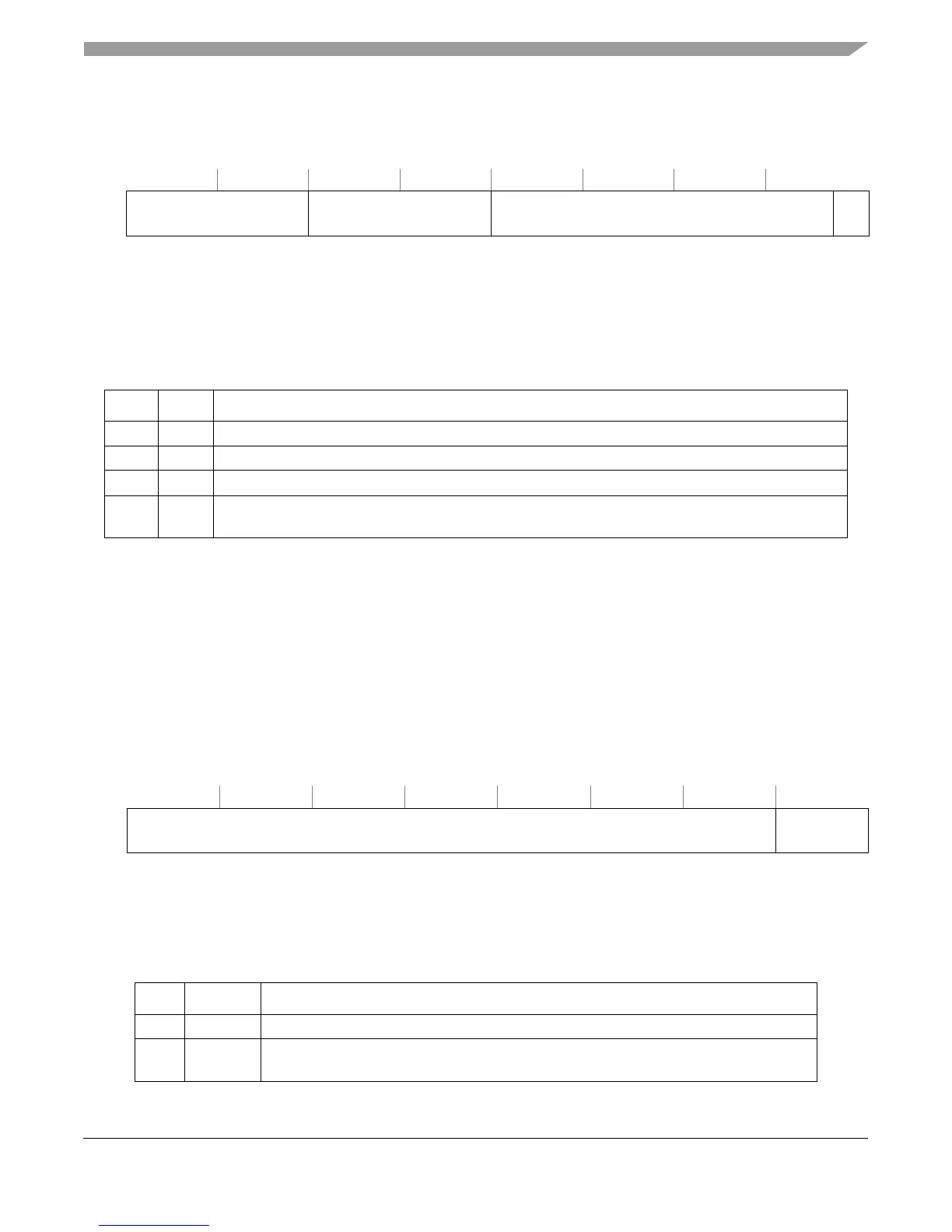

12.7.1.1 MAS Register 7 (MAS7)

The MAS7 register contains the high-order address bits of the RPN for implementations that

support more than 32 bits of physical address. (It contains 4 bits in the case of the e500v2.)

Implementations that do not support more than 32 bits of physical addressing do not implement

MAS7. Note that MAS7 can be automatically updated as a result of execution of tlbre and tlbsx

instructions (as is MAS3); this functionality is controlled by HID0[EN_MAS7_UPDATE].

Figure 12-17 shows the format of the MAS7 register.

The MAS7 fields are described in Table 12-14.

SPR 630 Access: Supervisor-only

32 39 40 47 48 62 63

R

—

SPID0 — SAS

W

Reset All zeros

Figure 12-16. MAS Register 6 (MAS6)

Table 12-13. MAS6—TLB Search Context Register 0

Bits Name Comments, or Function when Set

32–39 — Reserved, should be cleared.

40–47 SPID0 Specifies the PID value (recent value of PID0) used when searching the TLB during execution of tlbsx.

48–62 — Reserved, should be cleared.

63 SAS Address space (AS) value for searches. Specifies the value of AS used when searching the TLB (during

execution of tlbsx).

SPR 944 Access: Supervisor-only

32 59 60 63

R

—RPN

W

Reset All zeros

Figure 12-17. MAS Register 7 (MAS7)

Table 12-14. MAS7 Field Descriptions—High Order RPN

Bits Name Description

32–59 — Reserved, should be cleared.

60–63 RPN Real page number, 4 high-order bits. MAS3 holds only RPN[4–23]. The byte offset within

the page is provided by the EA and is not present in MAS3 or MAS7.

Loading...

Loading...