Memory Management Units

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 12-3

12.1.2 TLB Entry Maintenance Features

The TLB entries of the e500 core complex must be loaded and maintained by the system software;

this includes performing any required table search operations in memory. The e500 provides

support for maintaining TLB entries in software with the resources shown in Table 12-1. Note that

many of these features are defined at the Freescale Book E level.

t

Other hardware assistance features for maintenance of the TLBs on the e500 are described in

Section 12.5, “TLB Entry Maintenance—Details.”

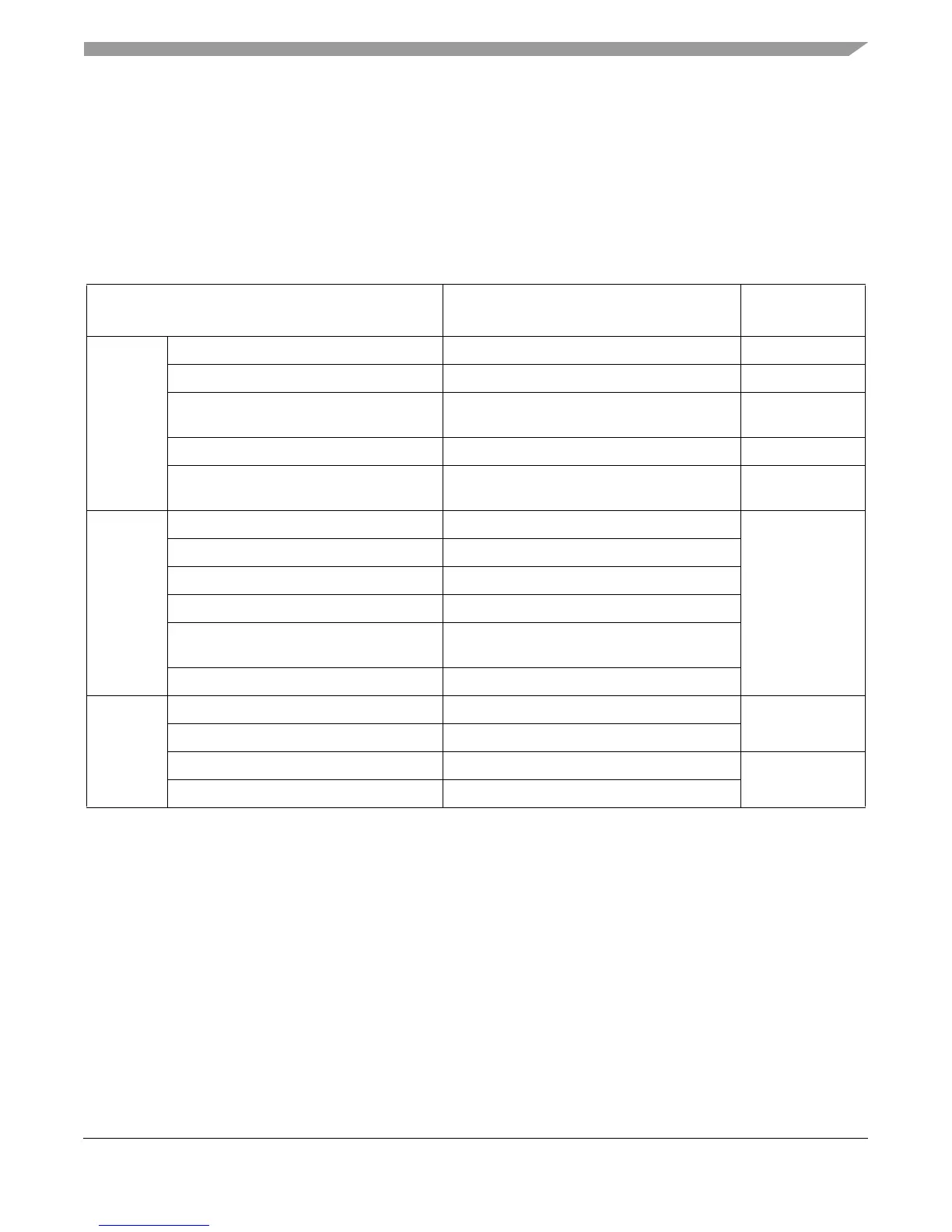

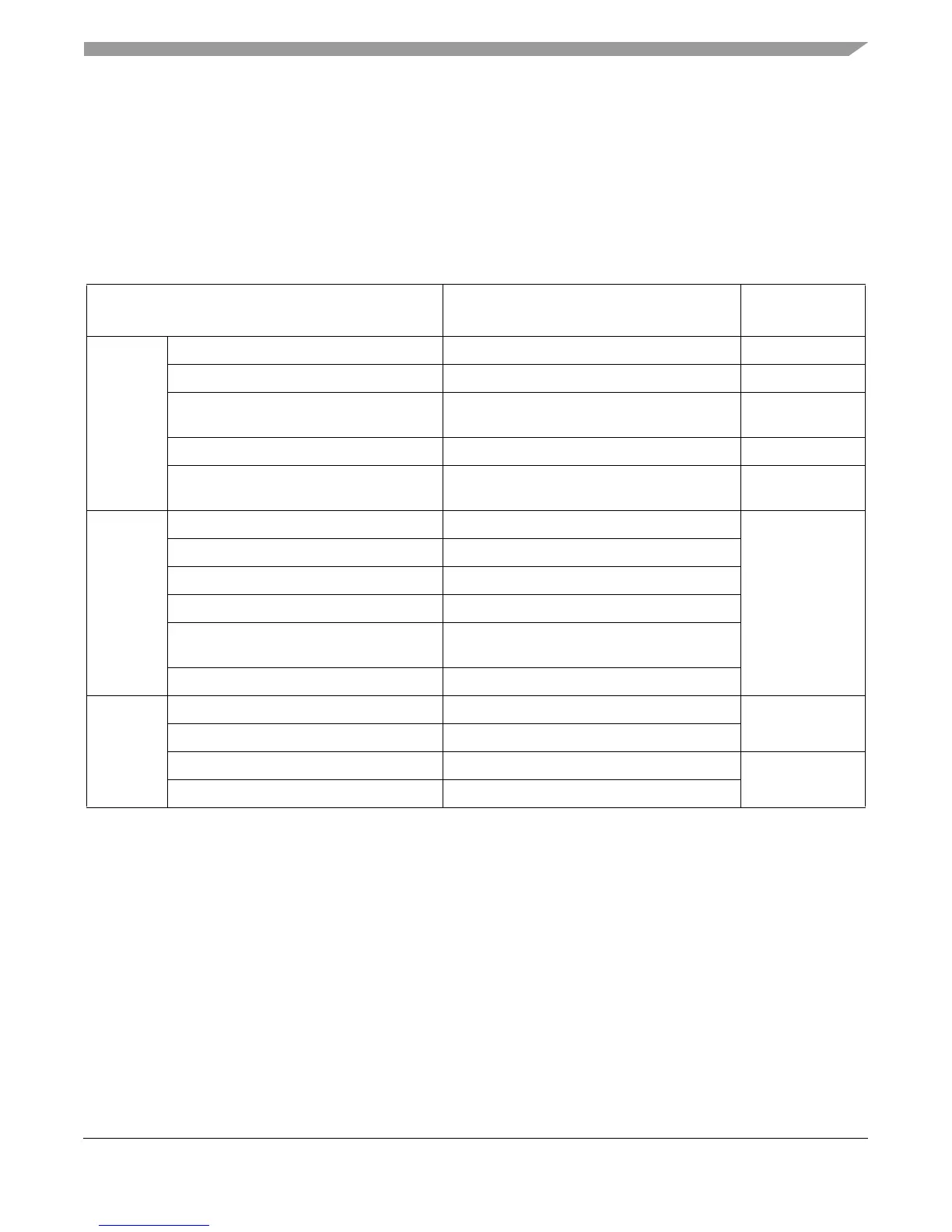

Table 12-1. TLB Maintenance Programming Model

Features Description

More Information

Section/Page

TLB

Instructions

tlbre TLB Read Entry instruction 12.4.1/12-18

tlbwe TLB Write Entry instruction 12.4.2/12-19

tlbsx rA, rB

(preferred form is tlbsx 0, rB)

TLB Search for entry instruction 12.4.3/12-19

tlbivax rA, rB TLB Invalidate entries instruction 12.4.4/12-20

tlbsync TLB Synchronize invalidations with other

masters’ instruction

12.4.5/12-22

Registers PID0–PID2 Process ID registers See Table 12-7 for

more

comprehensive

cross references

MMUCSR0 MMU control and status register

MMUCFG MMU configuration register

TLB0CFG–TLB1CFG TLB configuration registers

MAS0–MAS4, MAS6;

e500v2 also implements MAS7

MMU assist registers. Note that MAS5 is not

implemented on the e500.

DEAR Data exception address register

Interrupts Instruction TLB miss exception Causes instruction TLB error interrupt 12.5.1/12-23

Data TLB miss exception Causes data TLB error interrupt

Instruction permissions violation exception Causes ISI interrupt 12.5.2.1/12-24

Data permissions violation exception Causes DSI interrupt

Loading...

Loading...