PowerPC e500 Core Family Reference Manual, Rev. 1

5-20 Freescale Semiconductor

Interrupts and Exceptions

NOTE

icbi and icbt are treated as loads from the addressed byte with respect

to address translation and protection. They use MSR[DS], not

MSR[IS], to determine translation for their operands. Instruction

storage interrupts and instruction TLB error interrupts are associated

with instruction fetching and not execution. Data storage interrupts

and data TLB error interrupts are associated with the execution of

instruction cache management instructions.

When a data storage interrupt occurs, the processor suppresses execution of the instruction causing

the data storage exception. SRR0, SRR1, ESR, MSR, and DEAR, are updated as follows:

Instruction execution resumes at address IVPR[32–47] || IVOR2[48–59] || 0b0000.

5.7.4 Instruction Storage Interrupt

An instruction storage interrupt occurs when no higher priority exception exists and an instruction

storage exception is presented to the interrupt mechanism. Instruction storage exception

conditions are described in Table 5-13.

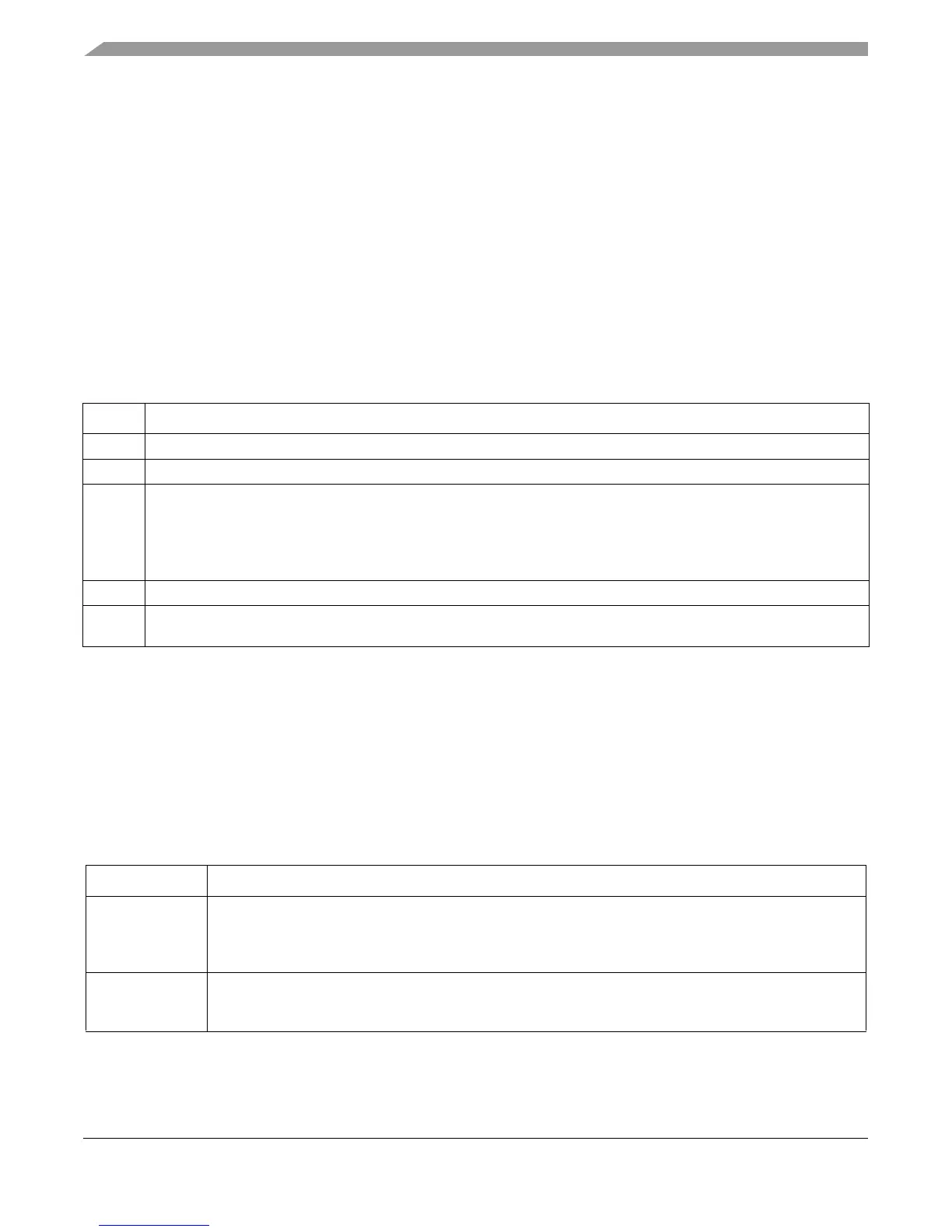

Table 5-12. Data Storage Interrupt Register Settings

Register Setting

SRR0 Set to the effective address of the instruction causing the interrupt

SRR1 Set to the MSR contents at the time of the interrupt

ESR ST Set if the instruction causing the interrupt is a store or store-class cache management instruction; otherwise

cleared

DLK DLK is set when a DSI occurs because dcbtls, dcbtstls, or dcblc is executed in user mode and MSR[UCLE] = 0.

BO Set if the instruction caused a byte-ordering exception; otherwise cleared

All other defined ESR bits are cleared.

MSR CE, ME, and DE are unchanged. All other MSR bits are cleared.

DEAR Set to the effective address of a byte that lies both within the range of bytes being accessed by the access or cache

management instruction and within the page whose access caused the exception

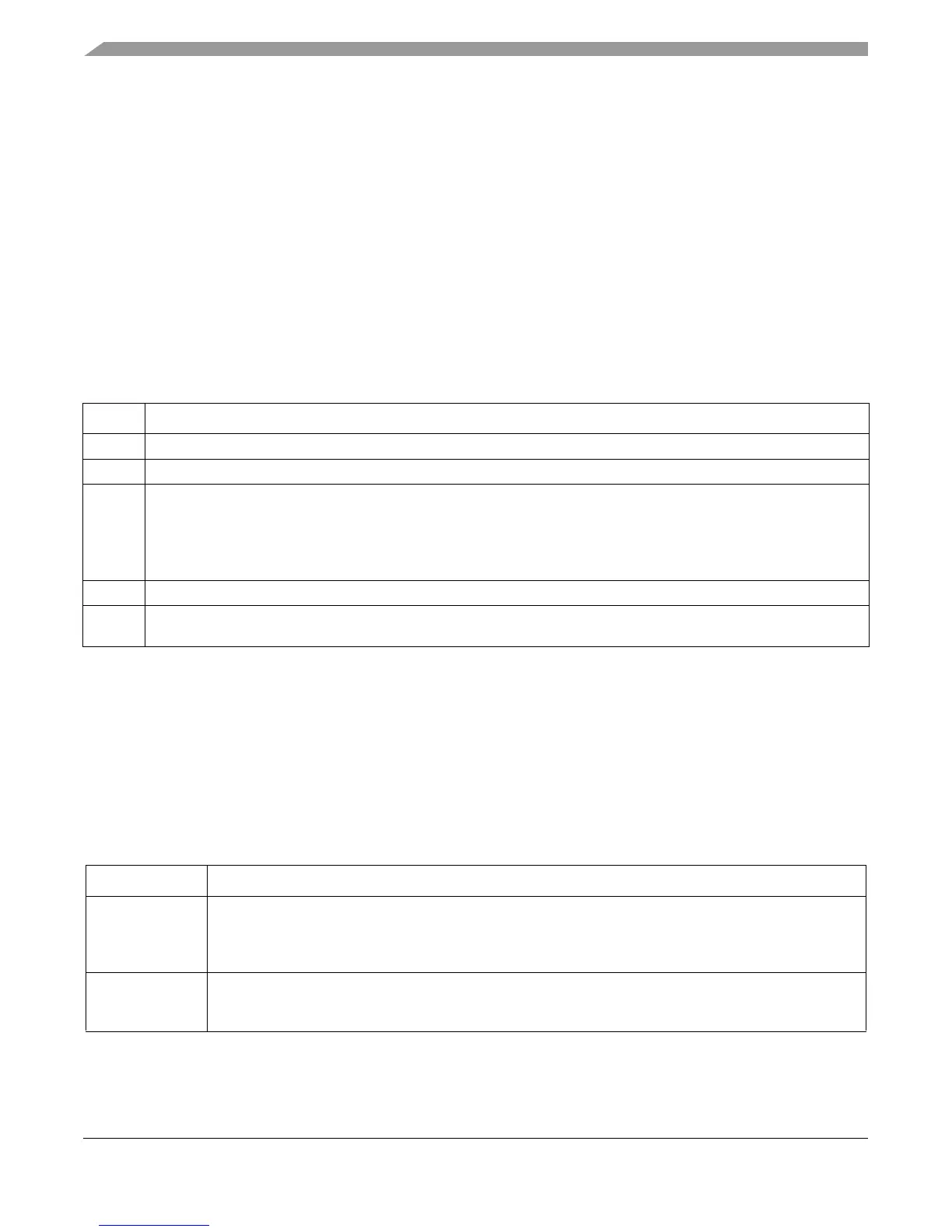

Table 5-13. Instruction Storage Interrupt Exception Conditions

Exception Cause

Execute access

control exception

In user mode, an instruction fetch attempts to access a memory location that is not user mode execute

enabled (page access control bit UX = 0).

In supervisor mode, an instruction fetch attempts to access a memory location that is not supervisor mode

execute enabled (page access control bit SX = 0).

Byte-ordering

exception

The implementation cannot fetch the instruction in the byte order specified by the page’s endian attribute.

The EIS defines that accesses that cross a page boundary such that endianness changes cause a

byte-ordering exception.

Loading...

Loading...