PowerPC e500 Core Family Reference Manual, Rev. 1

7-8 Freescale Semiconductor

Performance Monitor

7.2.7 Performance Monitor Counter Registers (PMC0–PMC3)

The performance monitor counter registers (PMC0–PMC3), shown in Figure 7-4, are 32-bit

counters that can be programmed to generate interrupt signals when they overflow. Each counter

is enabled to count up to 128 events.

PMCs are cleared by a hard reset. Table 7-6 describes PMC register fields.

The minimum counter value is 0x0000_0000; 4,294,967,295 (0xFFFF_FFFF) is the maximum. A

counter can increment by 0, 1, 2, 3, or 4 up to the maximum value and then wraps to the minimum

value.

A counter enters overflow state when the high-order bit is set by entering the overflow state at the

halfway point between the minimum and maximum values. A performance monitor interrupt

handler can easily identify overflowed counters, even if the interrupt is masked for many cycles

(during which the counters may continue incrementing). A high-order bit is set normally only

when the counter increments from a value below 2,147,483,648 (0x8000_0000) to a value greater

than or equal to 2,147,483,648 (0x8000_0000).

NOTE

Initializing PMCs to overflowed values is strongly discouraged. If an

overflowed value is loaded into a PMCn that held a non-overflowed

value (and PMGC0[PMIE], PMLCan[CE], and MSR[EE] are set), an

interrupt is generated before any events are counted.

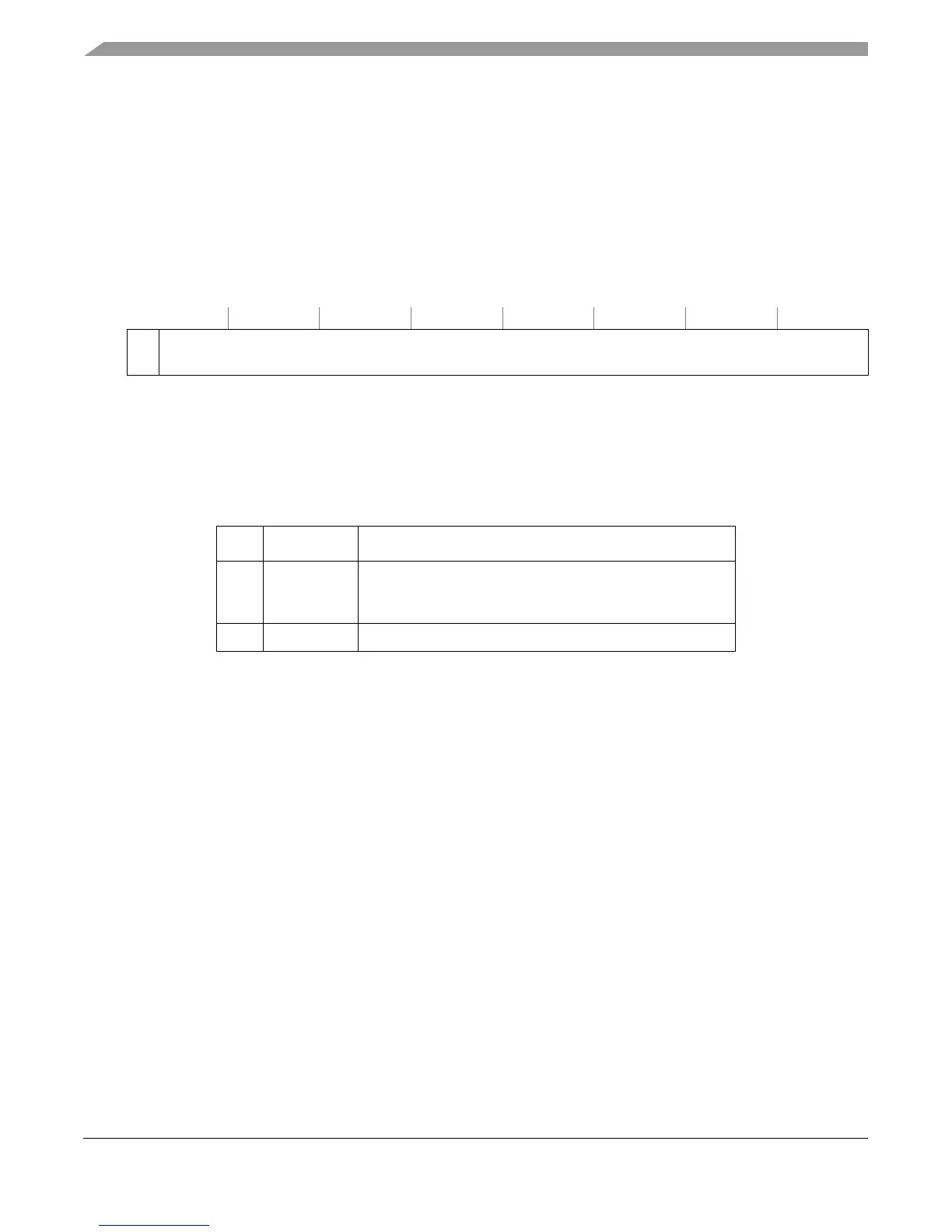

PMC0 (PMR16)

PMC1 (PMR17)

PMC2 (PMR18)

PMC3 (PMR19)

UPMC0 (PMR0)

UPMC1 (PMR1)

UPMC2 (PMR2)

UPMC3 (PMR3)

Access: PMC0–PMC3: Supervisor-only

UPMC0–UPMC3: Supervisor/user read-only

32 33 63

R

OV Counter value

W

Reset All zeros

Figure 7-4. Performance Monitor Counter Registers (PMC0–PMC3)/

User Performance Monitor Counter Registers (UPMC0–UPMC3)

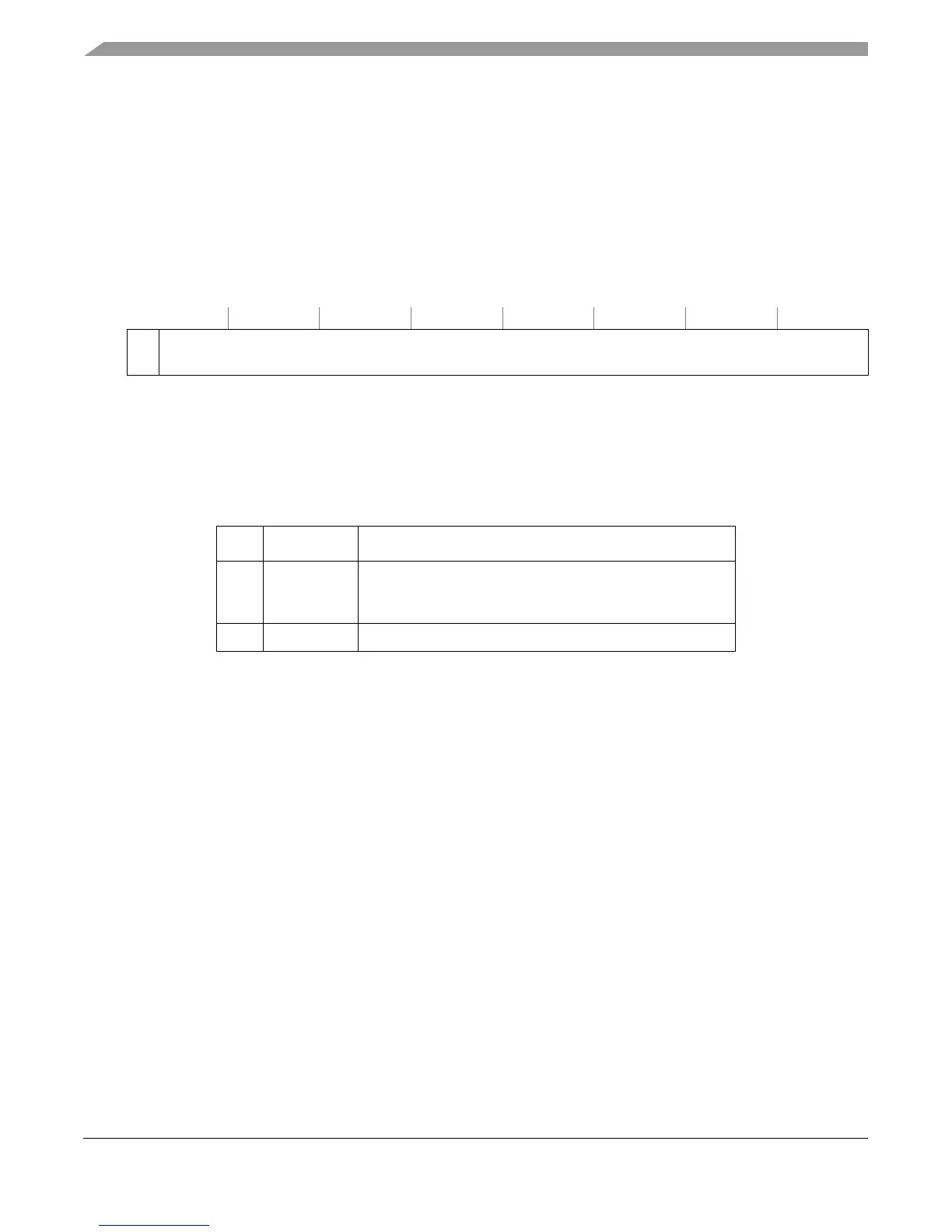

Table 7-6. PMC0–PMC3 Field Descriptions

Bits Name Description

32 OV Overflow.

0 Counter has not reached an overflow state.

1 Counter has reached an overflow state.

33–63 Counter Value Indicates the number of occurrences of the specified event.

Loading...

Loading...