PowerPC e500 Core Family Reference Manual, Rev. 1

3-30 Freescale Semiconductor

Instruction Model

3.3.1.6 Memory Synchronization Instructions

Memory synchronization instructions control the order in which memory operations complete

with respect to asynchronous events and the order in which memory operations are seen by other

mechanisms that access memory. See Section 3.3.1.7, “Atomic Update Primitives Using lwarx

and stwcx.,” for additional information about these instructions and about related aspects of

memory synchronization. See Table 3-25 for a summary.

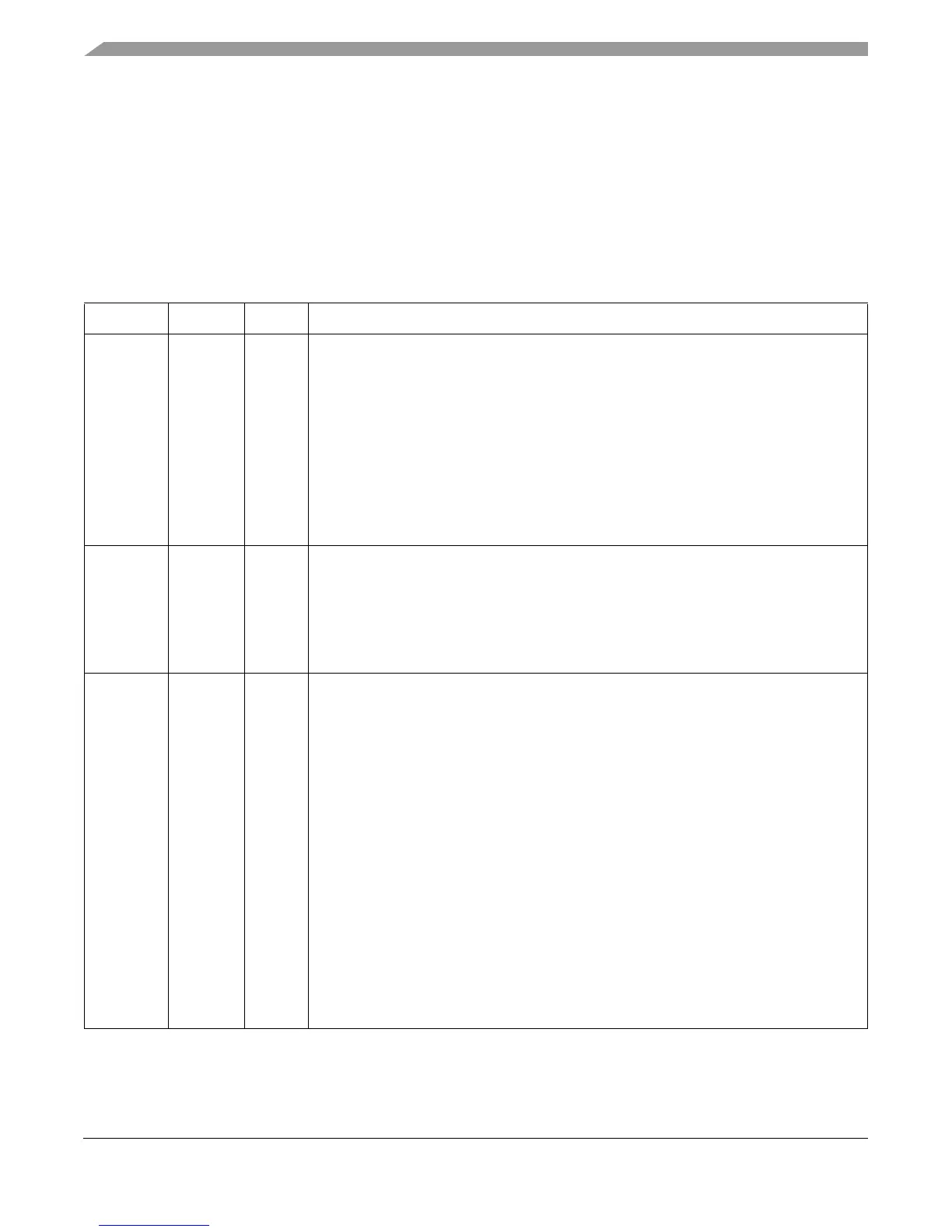

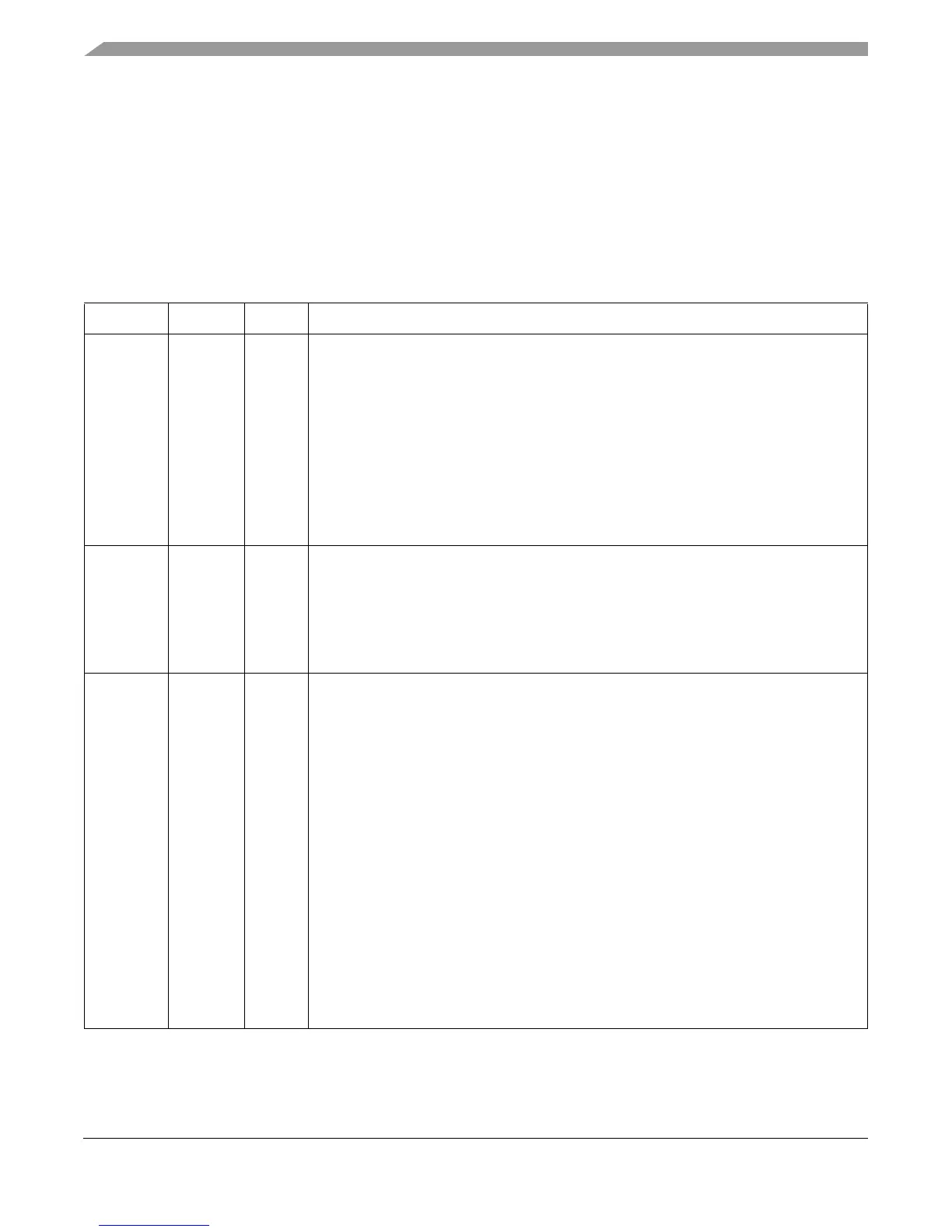

Table 3-25. Memory Synchronization Instructions

Name Mnemonic Syntax Implementation Notes

Instruction

Synchronize

isync — isync is refetch serializing; the e500 waits for previous instructions (including any interrupts

they generate) to complete before isync executes, which purges all instructions from the

core and refetches the next instruction. isync does not wait for pending stores in the store

queue to complete. Any subsequent instruction sees all effects of instructions before the

isync.

Because it prevents execution of subsequent instructions until preceding instructions

complete, if an isync follows a conditional branch instruction that depends on the value

returned by a preceding load, the load on which the branch depends is performed before

any loads caused by instructions after the isync even if the effects of the dependency are

independent of the value loaded (for example, the value is compared to itself and the

branch tests selected, CR

n

[EQ]), and even if the branch target is the next sequential

instruction to be executed.

Load Word

and

Reserve

Indexed

lwarx rD,rA,rB lwarx with stwcx. can emulate semaphore operations such as test and set, compare and

swap, exchange memory, and fetch and add. Both instructions must use the same EA.

Reservation granularity is implementation-dependent. The e500 makes reservations on

behalf of aligned 32-byte sections of address space. Executing lwarx and stwcx. to a page

marked write-through (WIMG = 10

xx

) or when the data cache is locked causes a data

storage interrupt. If the location is not word-aligned, an alignment interrupt occurs.

See Section 3.3.1.7, “Atomic Update Primitives Using lwarx and stwcx.”

Memory

Barrier

mbar MO mbar provides a memory barrier. (Note that mbar uses the same opcode as eieio, defined

by the Classic PowerPC architecture, and with which mbar (MO=1) is identical, as defined

by the EIS). The behavior of mbar depends on the value of MO operand.

MO ≠ 0—mbar instruction provides a storage ordering function for all memory access

instructions executed by the processor executing mbar. Executing mbar ensures that all

data storage accesses caused by instructions preceding the mbar have completed before

any data storage accesses caused by any instructions after the mbar. This order is seen

by all mechanisms.

MO = 1—The EIS defines mbar to function identically to eieio, as defined by the classic

PowerPC architecture. For more information, see Section 3.3.1.6.1, “mbar (MO = 1).”

The following sequence shows one use of mbar in supporting shared data, ensuring the

action is completed before the lock is released.

P1 P2

lock . . .

read & write . . .

mbar . . .

free lock . . .

. . . lock

. . . read & write

. . . mbar

. . . free lock

Loading...

Loading...