PowerPC e500 Core Family Reference Manual, Rev. 1

5-12 Freescale Semiconductor

Interrupts and Exceptions

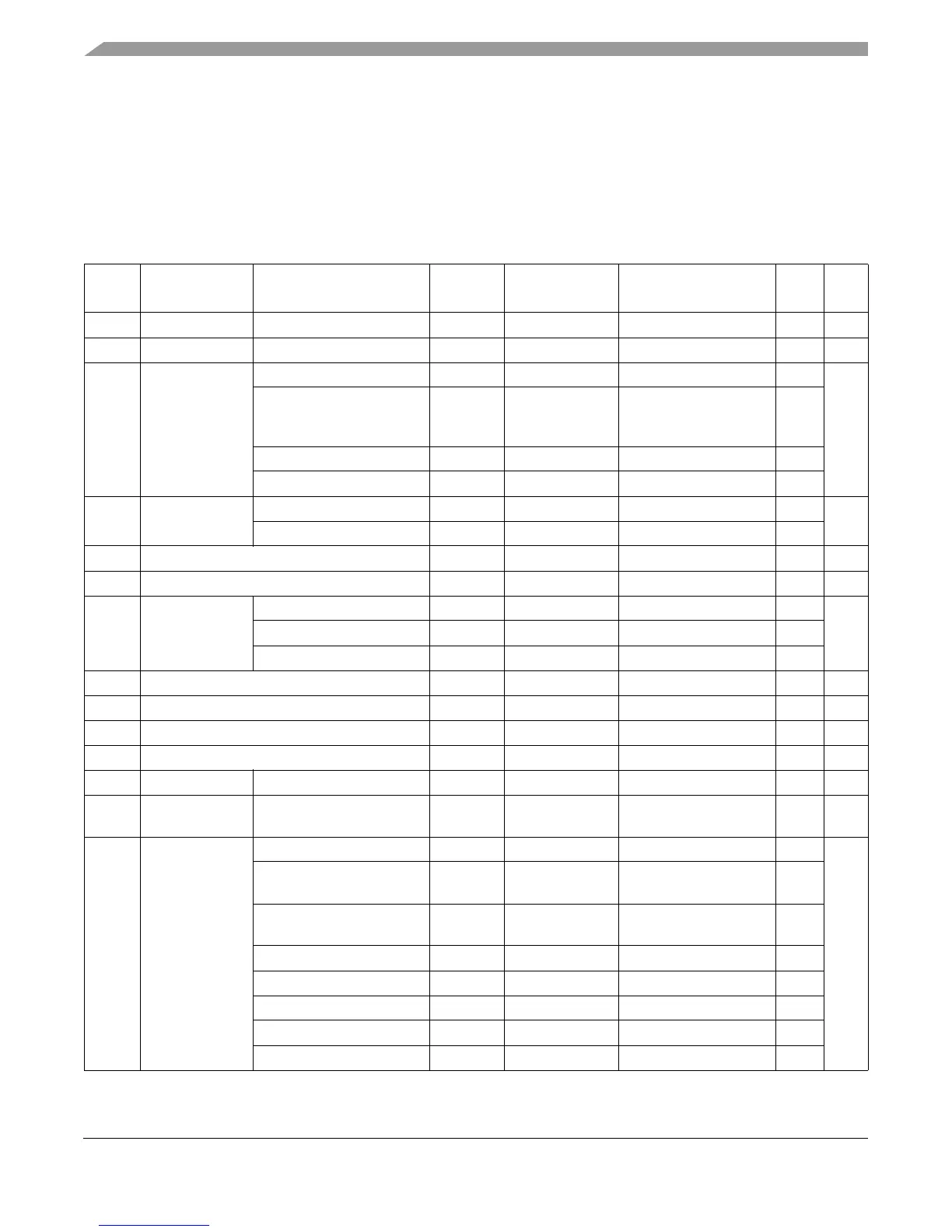

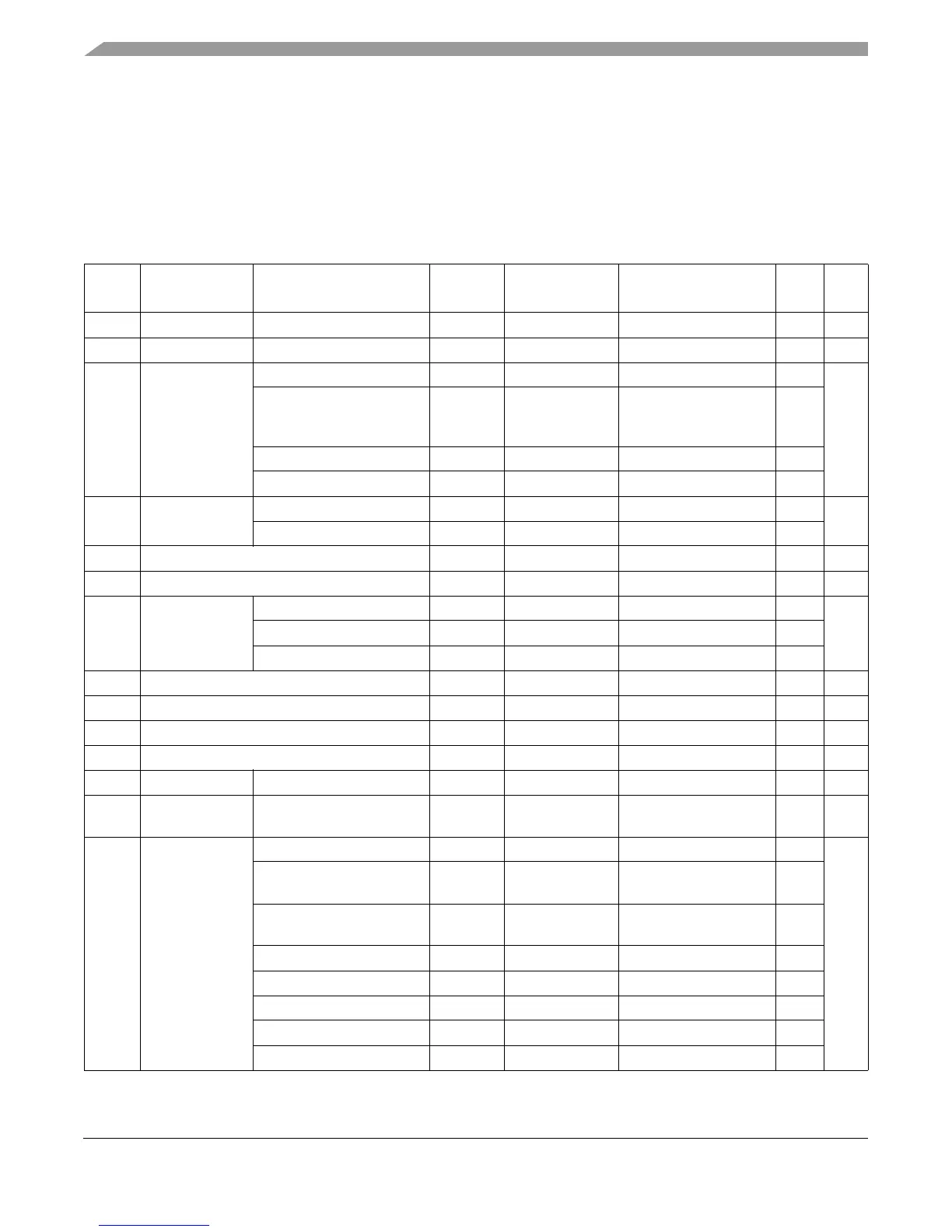

5.7 Interrupt Definitions

Table 5-6 summarizes each interrupt type, the various exception types that may cause that

interrupt, the interrupt classification, which ESR bits can be set, which MSR bits can mask the

interrupt type, and which IVOR is used to specify the vector address.

Table 5-6. Interrupt and Exception Types

IVOR Interrupt Type Exception Type

Exception

Class

1

ESR

2

Mask Bits Notes Page

IVOR0 Critical input Critical input A, C — MSR[CE]

3

5-13

IVOR1 Machine check Machine check C — MSR[ME]

4,5

5-14

IVOR2 Data storage

(DSI)

Access SP [SPE],[ST] —

6

5-19

Load reserve or store

conditional to write- through

required location (W = 1)

SP [ST] —

6

Cache locking SP [DLK,ILK],[ST] —

7

Byte ordering SP [ST],BO — —

IVOR3 Instruction

storage (ISI)

Access SP — — — 5-20

Byte ordering SP BO — —

IVOR4 External input A — MSR[EE]

3

5-21

IVOR5 Alignment SP [ST],[SPE,ST] — — 5-22

IVOR6 Program Illegal SP PIL — — 5-24

Privileged SP PPR — —

Trap SP PTR — —

IVOR8 System call SP — — — 5-25

IVOR10 Decrementer A — MSR[EE], TCR[DIE] — 5-25

IVOR11 Fixed interval timer A — MSR[EE], TCR[FIE] — 5-26

IVOR12 Watchdog A, C — MSR[CE], TCR[WIE] — 5-27

IVOR13 Data TLB error Data TLB miss SP [SPE],[ST] — — 5-27

IVOR14 Instruction TLB

error

Instruction TLB miss SP — — — 5-29

IVOR15 Debug Trap (synchronous) A, SP, C — MSR[DE], DBCR0[IDM] — 5-30

Instruction address

compare (synchronous)

A, SP, C — MSR[DE], DBCR0[IDM] —

Data address compare

(synchronous)

A, SP, C — MSR[DE], DBCR0[IDM] —

Instruction complete SP, C — MSR[DE], DBCR0[IDM]

8

Branch taken SP, C — MSR[DE], DBCR0[IDM]

8

Return from interrupt SP, C — MSR[DE], DBCR0[IDM] —

Interrupt taken SI, C — MSR[DE], DBCR0[IDM] —

Unconditional debug event SI, C — MSR[DE], DBCR0[IDM] —

Loading...

Loading...