Interrupts and Exceptions

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 5-29

Instruction execution resumes at address IVPR[32–47] || IVOR13[48–59] || 0b0000.

5.7.13 Instruction TLB Error Interrupt

An instruction TLB error interrupt occurs when no higher priority exception exists and the

exception described in Table 5-26 is presented to the interrupt mechanism.

When an instruction TLB error interrupt occurs, the processor suppresses execution of the

instruction causing the instruction TLB miss exception.

SRR0, SRR1, and MSR are updated as shown in Table 5-27.

Table 5-25 shows MAS register settings for data and instruction TLB error interrupts as

implemented on the e500. The “Cache and MMU Background” chapter of the EREF describes

how these values are set as defined by the EIS.

Instruction execution resumes at address IVPR[32–47] || IVOR14[48–59] || 0b0000.

WD, ID, MD, GD, ED —

SPID0 PID0

SAS MSR[IS] for instruction access;

MSR[DS] for data access

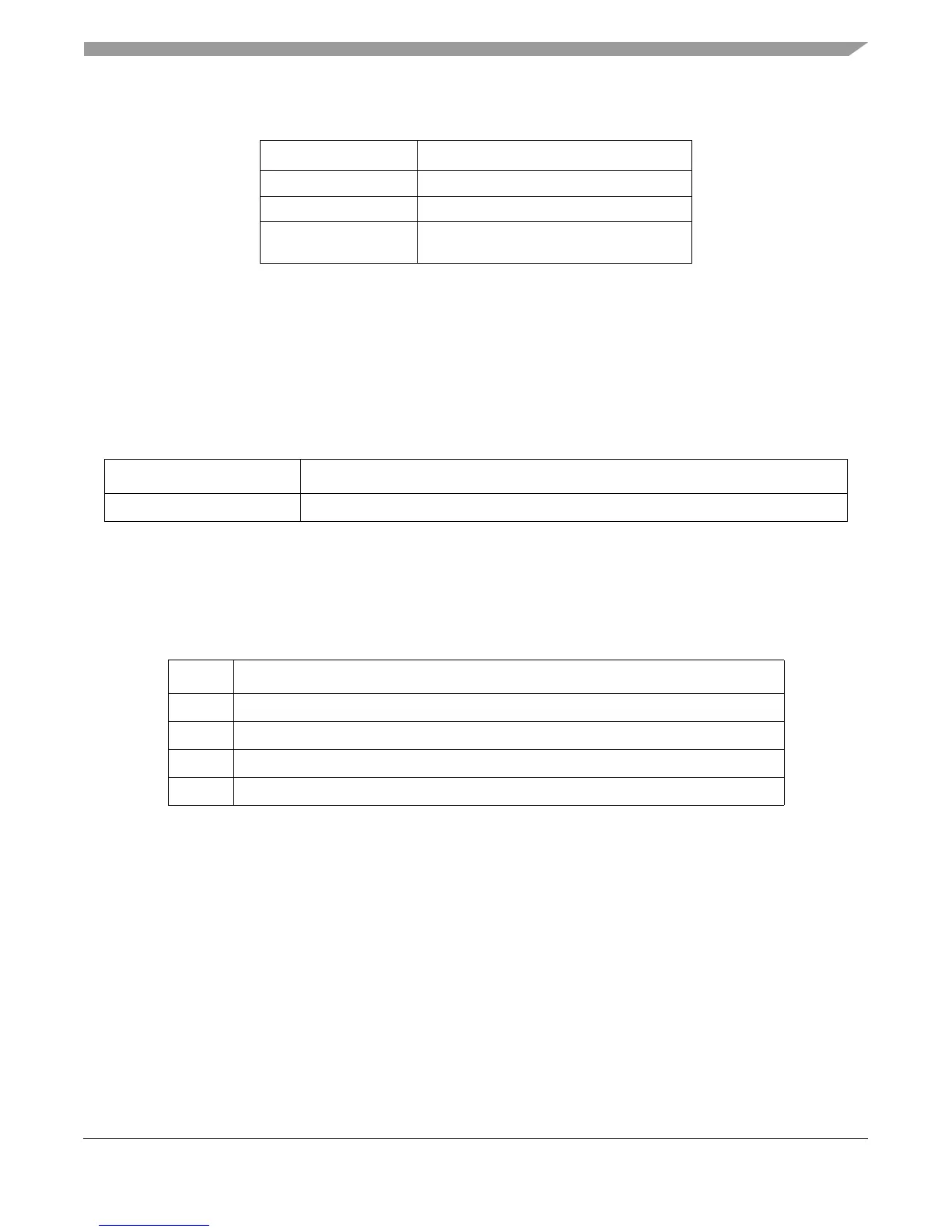

Table 5-26. Instruction TLB Error Interrupt Exception Conditions

Exception Description

Instruction TLB miss exception Virtual addresses associated with an instruction fetch do not match any valid TLB entry.

Table 5-27. Instruction TLB Error Interrupt Register Settings

Register Setting

SRR0 Set to the effective address of the instruction causing the instruction TLB error interrupt.

SRR1 Set to the MSR contents at the time of the interrupt.

MSR CE, ME, and DE are unchanged. All other MSR bits are cleared.

MAS

n

See Table 5-25.

Table 5-25. MMU Assist Register Field Updates for TLB Error Interrupts (continued)

MAS Register Bit/Field Value Loaded for Each Case

Loading...

Loading...