Register Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 2-13

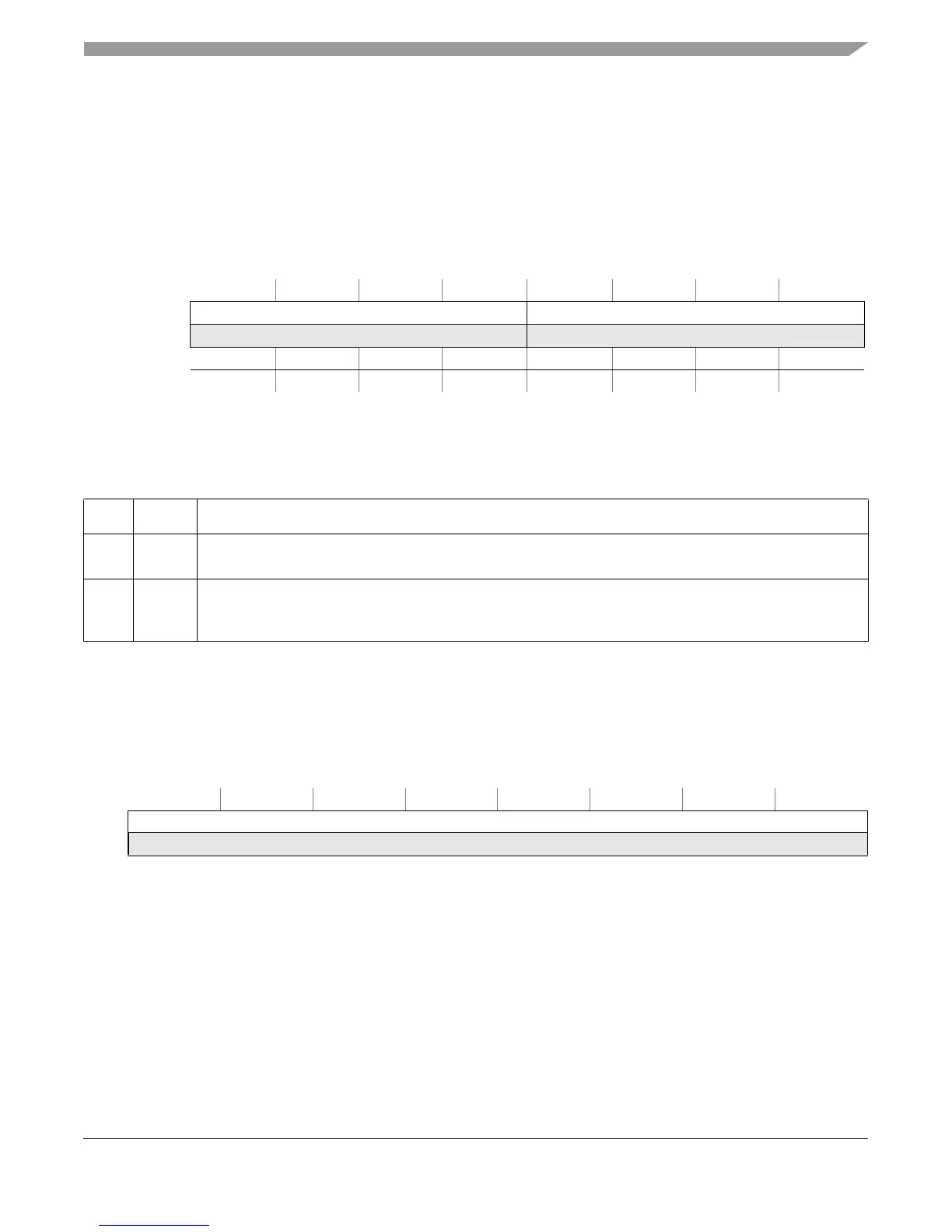

2.5.3 Processor Version Register (PVR)

The e500 implements the processor version register (PVR) as defined by the Book E architecture.

The read-only PVR, shown in Figure 2-3, contains a value identifying the version and revision

level of the processor. The PVR distinguishes between processors that differ in attributes that may

affect software.

Table 2-4 describes the PVR fields.

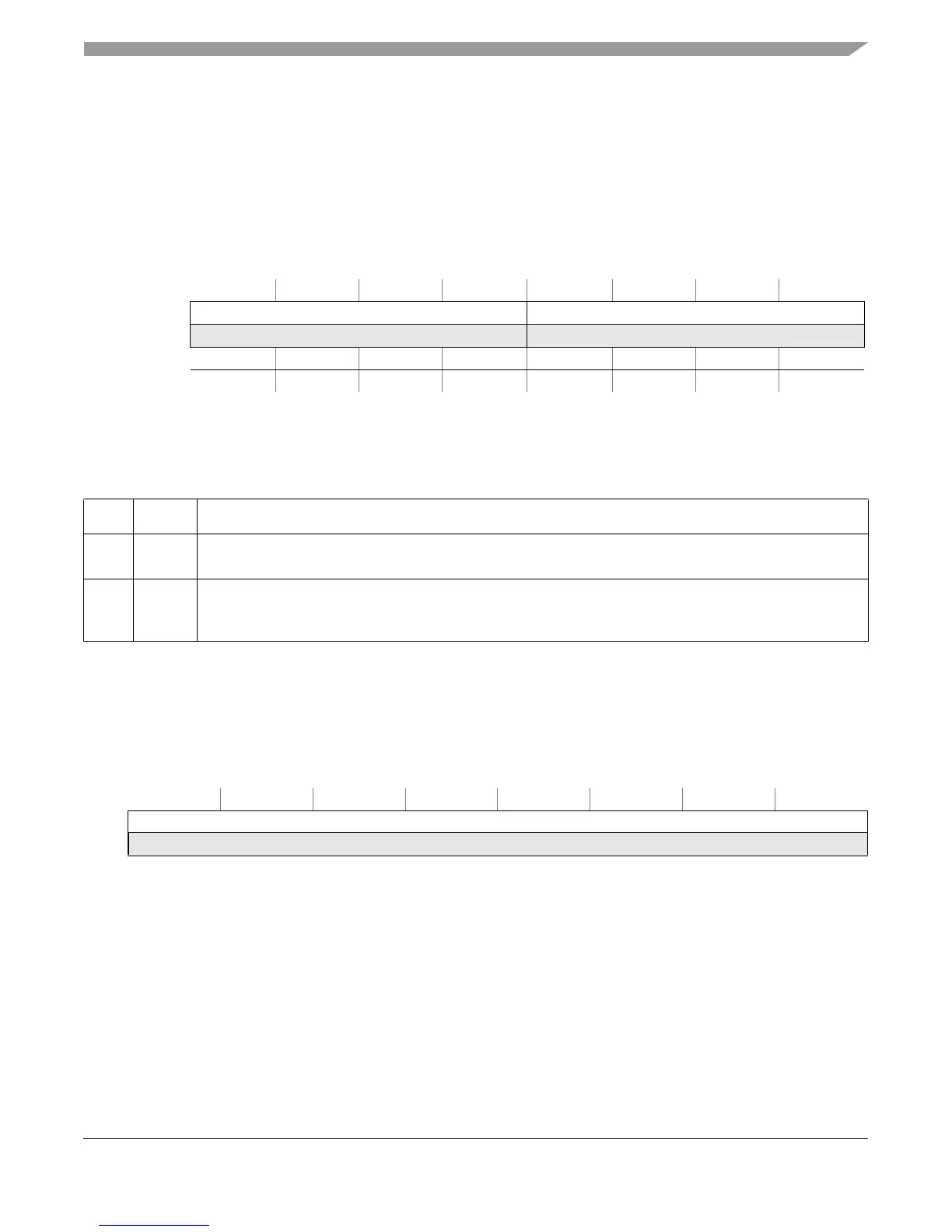

2.5.4 System Version Register (SVR)

The system version register (SVR), shown in Figure 2-4, contains a read-only SoC-dependent

value; consult the documentation for the implementation.

SPR 287 Access: Supervisor read-only

32 47 48 63

R Versi on Revision

W

Reset(e500v1) 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0

Reset (e500v2) 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0

Figure 2-3. Processor Version Register (PVR)

Table 2-4. PVR Field Descriptions

Bits Name Description

32–47 Version A 16-bit number that identifies the version of the processor. Different version numbers indicate major

differences between processors, such as which optional facilities and instructions are supported.

48–63 Revision A 16-bit number that distinguishes between implementations of the version. Different revision numbers

indicate minor differences between processors having the same version number, such as clock rate and

engineering change level.

SPR 1023 Access: Supervisor read-only

32 63

R System version

W

Reset SoC-dependent value (determined by

svr

[0:31]. See Section 13.2, “Signal Summary.”)

Figure 2-4. System Version Register (SVR)

Loading...

Loading...