Memory Management Units

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 12-25

Note also that because the core complex fetches from effective address 0xFFFF_FFFC out of reset,

the first access out of reset is automatically translated with this default TLB entry. The instruction

located at 0xFFFF_FFFC should be a branch instruction to the beginning of this 4-Kbyte page.

Because this default entry only translates a 4-Kbyte page, the initial code in this page needs to set

up more valid TLB entries (and pages) so that the program can branch out of this 4-Kbyte page

into other pages for booting the operating system. In particular, the interrupt vector area and the

pages that contain the interrupt handlers should be set up so that exceptions can be handled early

in the booting process.

12.7 Core Complex MMU Registers

Table 12-7 provides cross-references to other sections that have more detailed bit descriptions for

the e500 registers related to the MMU. Also, the EREF lists the Freescale Book E definitions for

these registers.

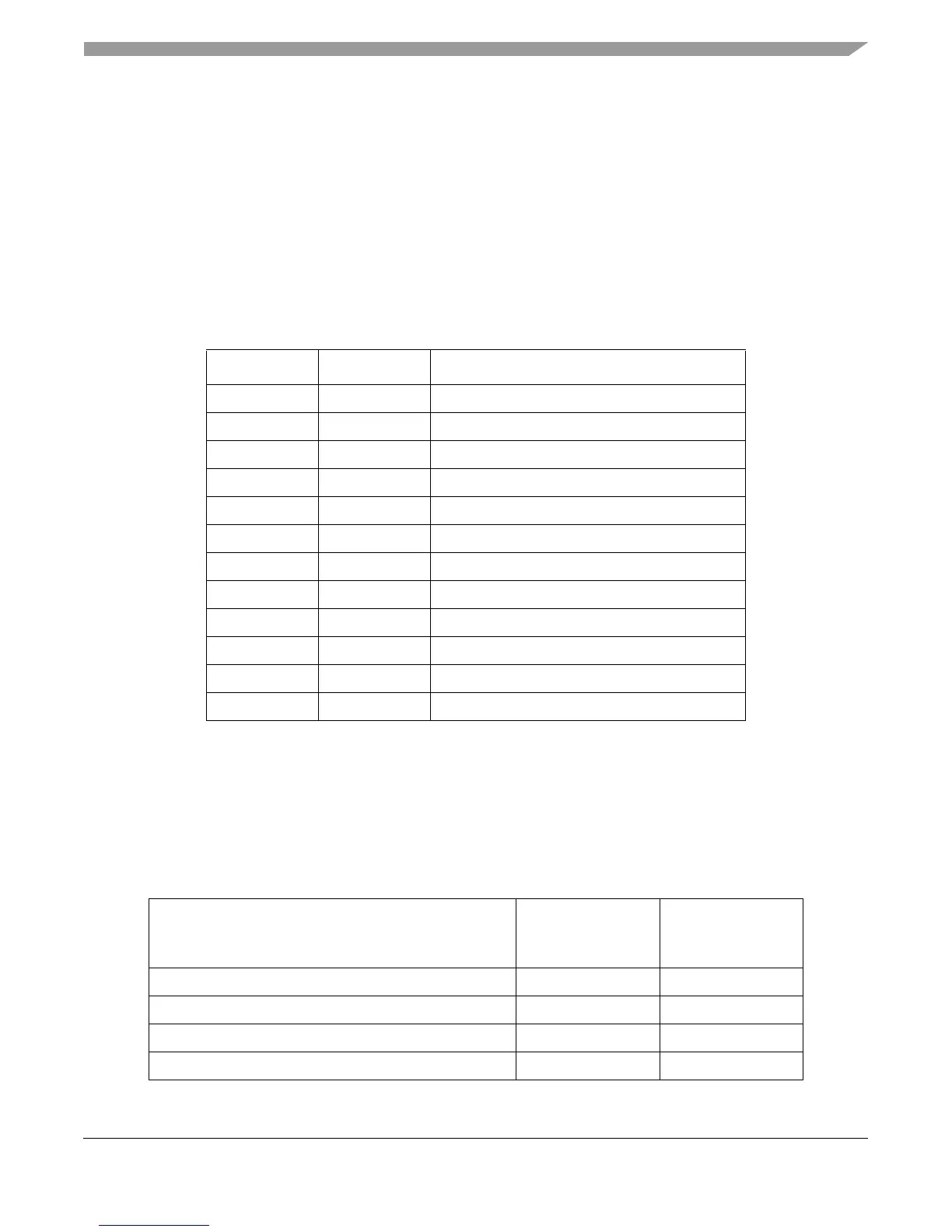

Table 12-6. TLB1 Entry 0 Values after Reset

Field Reset Value Comments

V 1 Entry is valid

TS 0 Address space 0

TID[0–7] 0x00 TID value for shared (global) page

EPN[32–51] 0xFFFFF Address of last 4-Kbyte page in address space

RPN[32–51] 0xFFFFF Address of last 4-Kbyte page in address space

SIZE[0–3] 0001 4-Kbyte page size

SX/SR/SW 111 Full supervisor mode access allowed

UX/UR/UW 000 No user mode access allowed

WIMGE 01000 Caching-inhibited, non-coherent, big-endian

X0–X1 00 Reserved system attributes

U0–U3 0000 User attribute bits

IPROT 1 Page is protected from invalidation

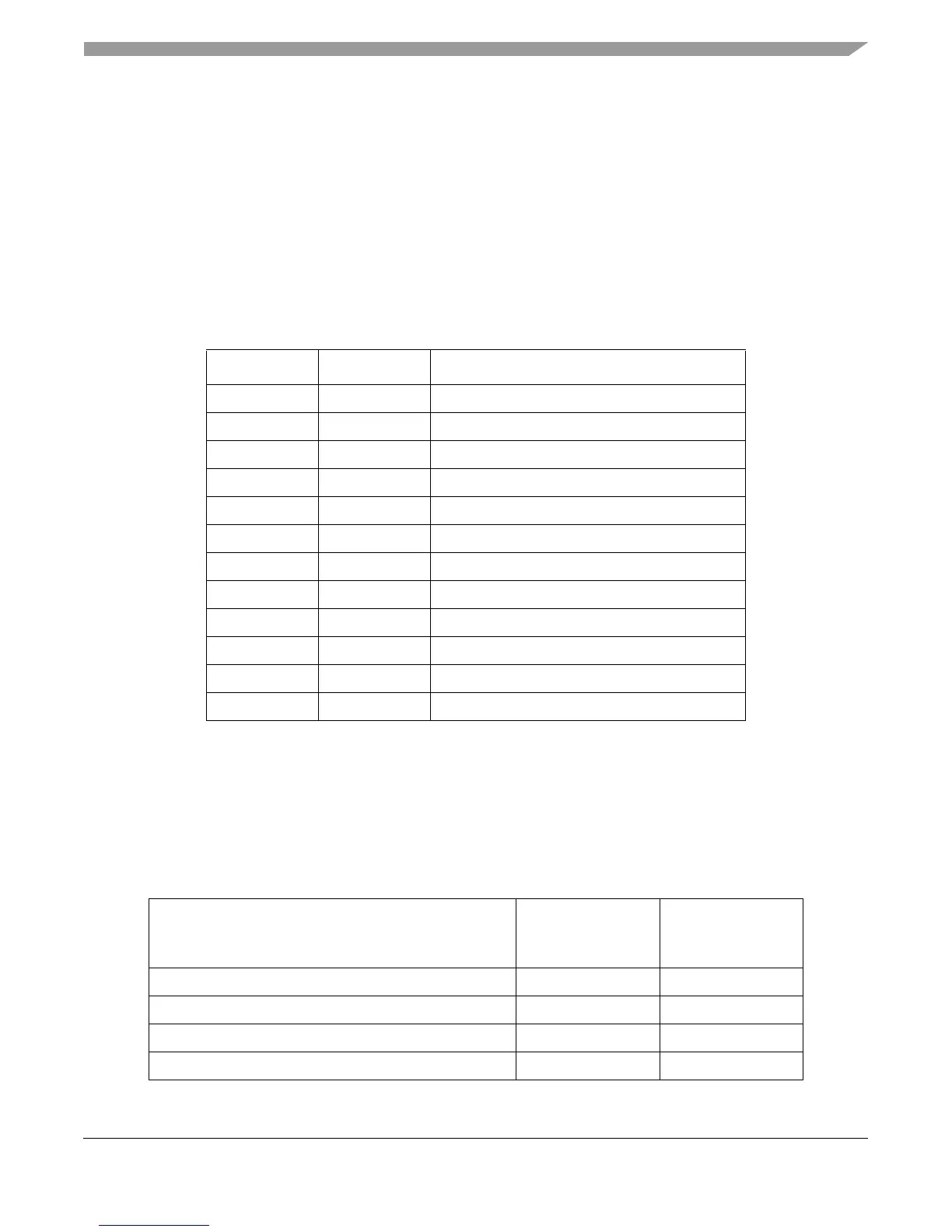

Table 12-7. Registers Used for MMU Functions

Registers

Comprehensive

Reference

(Section/Page)

Additional

e500-Only Reference

(Section/Page)

Process ID (PID0–PID2) 2.12.1/2-36 —

MMU control and status register (MMUCSR0) 2.12.2/2-36 —

MMU configuration register (MMUCFG) 2.12.3/2-37 —

TLB configuration registers (TLB0CFG–TLB1CFG) 2.12.4/2-37 —

Loading...

Loading...