PowerPC e500 Core Family Reference Manual, Rev. 1

11-16 Freescale Semiconductor

L1 Caches

If the reservation has been canceled for any reason, then stwcx. fails and clears CR0[EQ]. The

architectural intent is to follow the lwarx/stwcx. instruction pair with a conditional branch that

checks whether stwcx. failed.

The state of the reservation coherency bit is always signaled. This can be used to determine when

an internal condition caused the coherency bit to be reset.

The reservation is invalidated when any asynchronous interrupt is signaled. External interrupts

and watchdog timer interrupts are examples of asynchronous interrupts.

11.4 L1 Cache Control

The core complex L1 caches are controlled by programming specific L1CSRn bits and by issuing

dedicated cache control instructions. Section 11.4.1, “Cache Control Instructions,” describes the

cache control instructions and gives implementation-specific information. The remainder of this

section describes how the cache control instructions and the L1CSRn bits are used to control the

L1 cache.

11.4.1 Cache Control Instructions

The following instructions can be used for management of the e500 L1 caches—dcba, dcbf, dcbi,

dcblc, dcbst, dcbt, dcbtls, dcbtst, dcbtstls, dcbz, icbi, icblc, icbt, and icbtls.

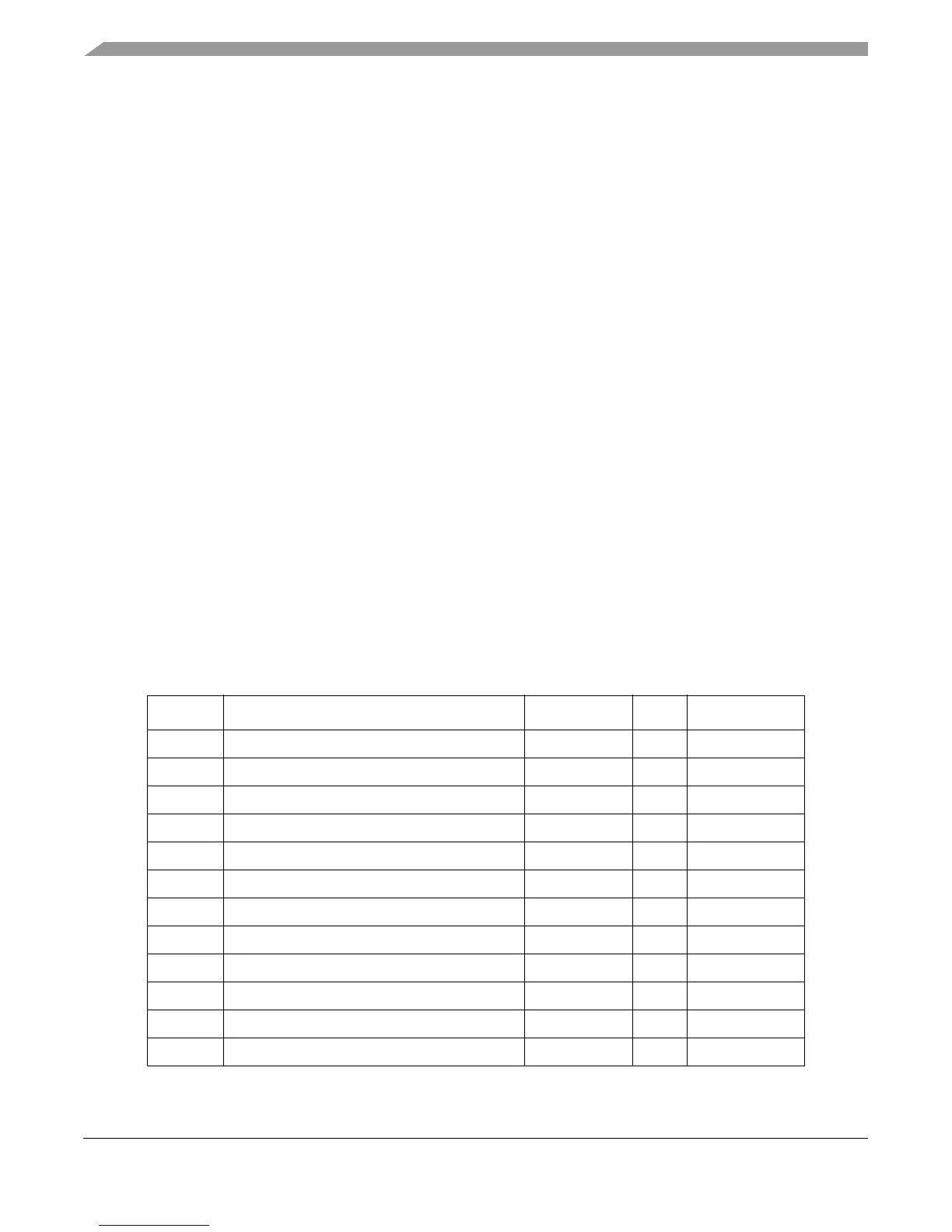

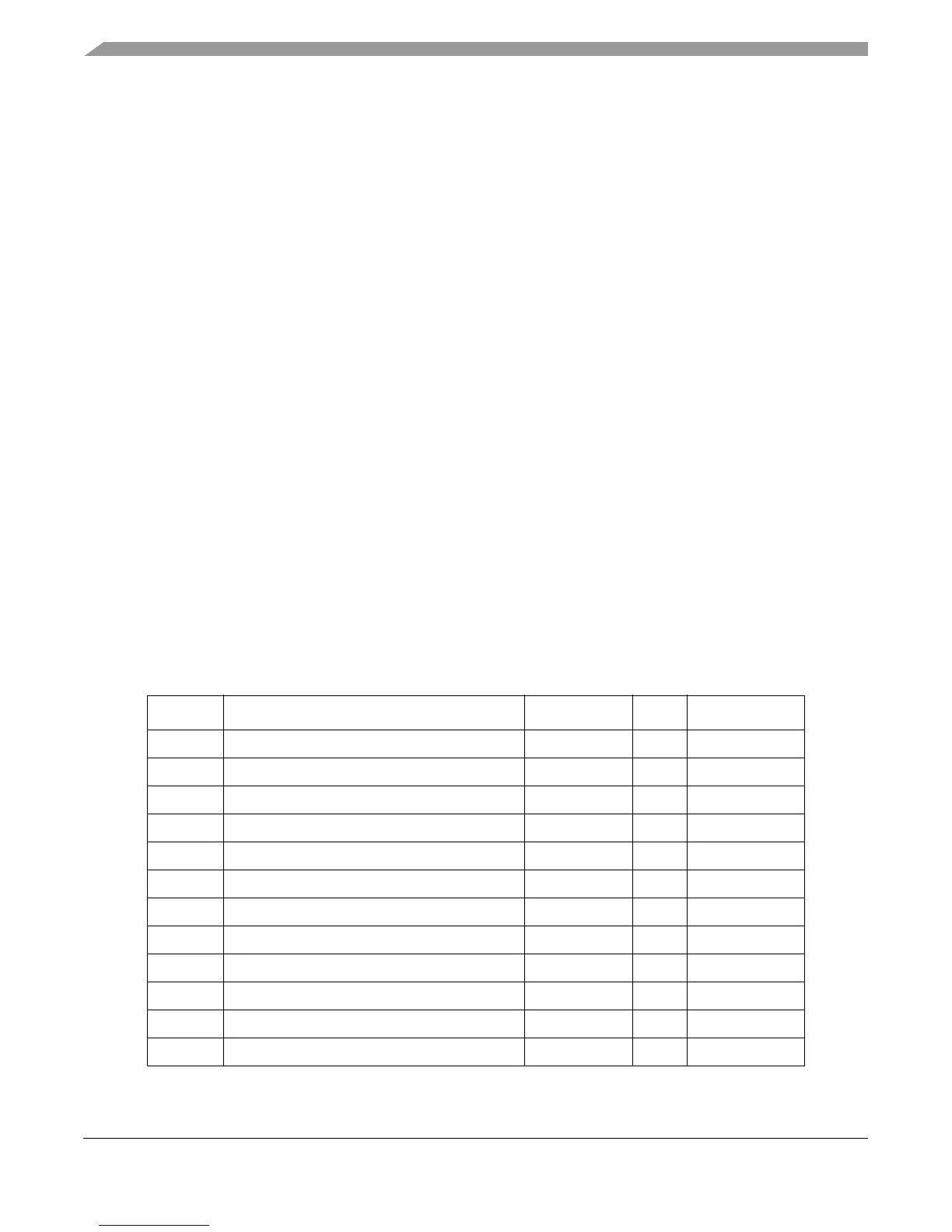

Table 11-6 shows how cache-control instructions apply to the e500 core, Book E architecture, and

the AIM definition of the PowerPC architecture.

Table 11-6. Cache Instruction Comparison

Mnemonic Instruction e500 Core Book E AIM Architecture

dcba Data Cache Block Allocate x x x

dcbf Data Cache Block Flush x x x

dcbi Data Cache Block Invalidate x x x

dcblc Data Cache Block Lock Clear x

dcbst Data Cache Block Store mapped to dcbf xx

dcbt Data Cache Block Touch x x x

dcbtls Data Cache Block Touch and Lock Set x

dcbtst Data Cache Block Touch for Store x x x

dcbtstls Data Cache Block Touch for Store and Lock Set x

dcbz Data Cache Block Zero x x x

icbi Instruction Cache Block Invalidate x x x

icblc Instruction Cache Block Lock Clear x

Loading...

Loading...