Memory Management Units

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 12-9

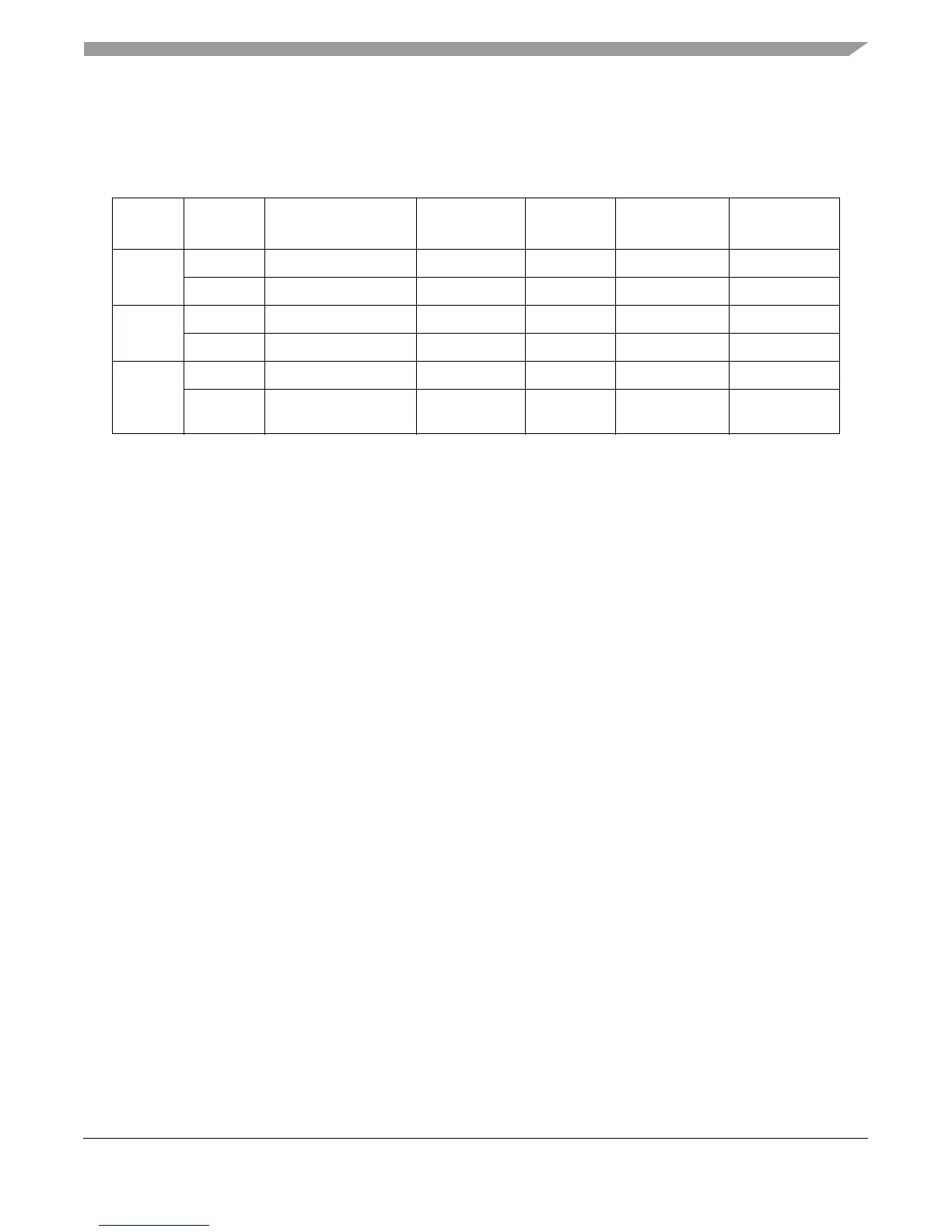

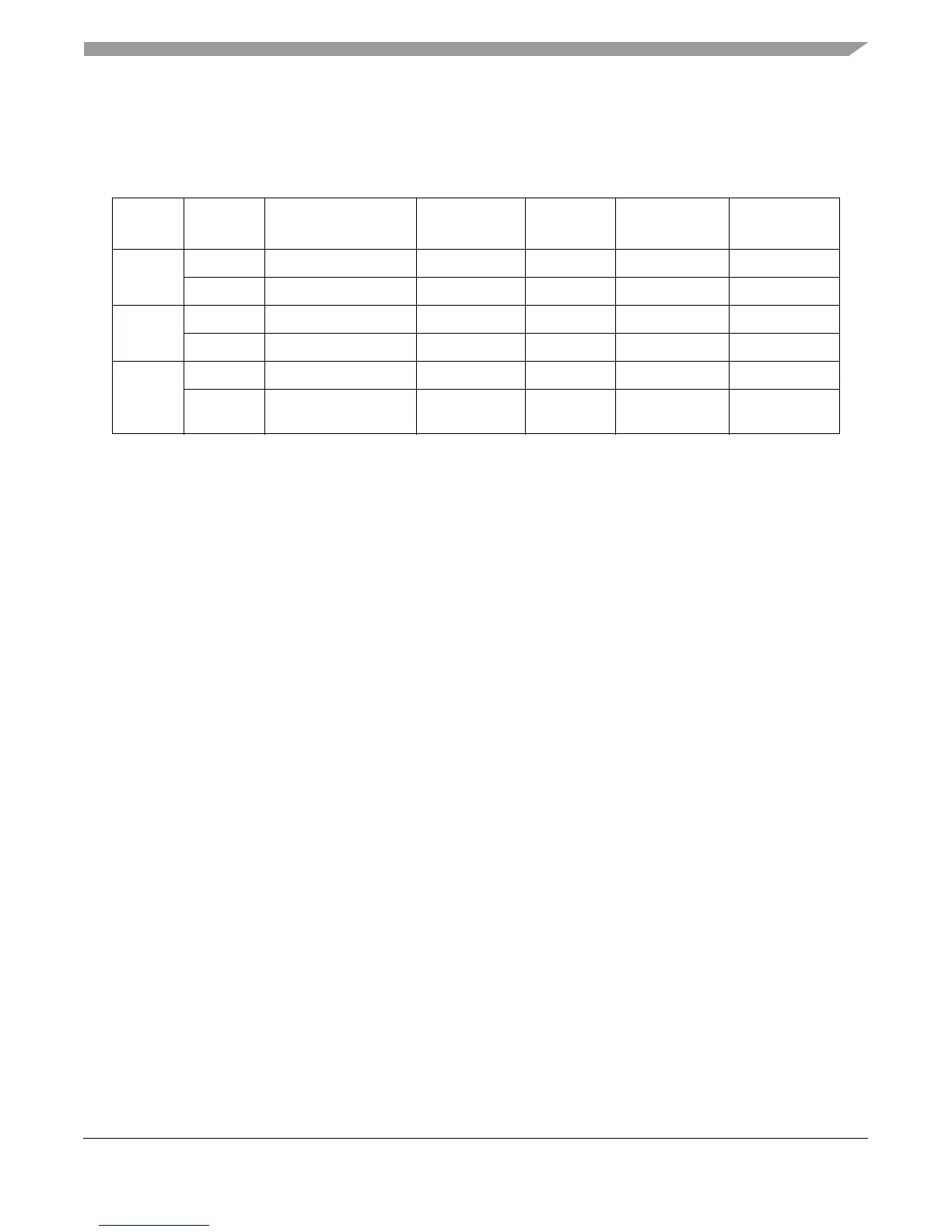

Table 12-3 lists the various TLBs and describes their characteristics. Note that the e500v2 supports

eleven page sizes (as shown in parentheses).

12.3.1 L1 TLB Arrays

As shown in Figure 12-1, there are two level 1 (L1) MMUs in the core complex. As shown in

Figure 12-4 and Table 12-3, the instruction and data L1 MMUs each implement a 4-entry, fully

associative L1VSP array and a 64-entry, 4-way set associative L1TLB4K array, comprising the

following L1 MMU arrays:

• Instruction L1VSP—4-entry, fully-associative

• Instruction L1TLB4K—64-entry, 4-way set-associative

• Data L1VSP—4-entry, fully associative

• Data L1TLB4K—64-entry, 4-way set-associative

As their names imply, the L1TLB4K arrays only support a 4-Kbyte page size while the L1VSP

arrays support nine (e500v1) or eleven (e500v2) page sizes. To perform a lookup for instruction

accesses, both the L1TLB4K and the L1VSP TLBs in the instruction MMU are searched in parallel

for the matching TLB entry. Similarly, for data accesses, both the L1TLB4K and the L1VSP TLBs

in the data MMU are searched in parallel for the matching TLB entry. The contents of a matching

TLB entry are then concatenated with the page offset of the original effective address; the bit range

that is translated is determined by the page size. The result constitutes the real (physical) address

for the access.

Table 12-3. Index of TLBs

Location Name Page Sizes Supported Associativity

Size of TLB

(# of entries)

Instruction/Data

Translations

Filled by

Instruction

L1 MMU

I-L1VSP 9 (or 11) page sizes

1

1

See Tabl e 12 - 2 for supported page sizes.

Fully associative 4 Instruction TLB1 hit

I-L1TLB4K 4 Kbyte 4-way 64 Instruction TLB0 hit

Data

L1 MMU

D-L1VSP 9 (or 11) page sizes

1

Fully associative 4 Data TLB1 hit

D-L1TLB4K 4 Kbyte 4-way 64 Data TLB0 hit

L2 MMU TLB1 9 (or 11) page sizes

1

Fully associative 16 Unified (I and D) tlbwe instruction

TLB0 4 Kbyte 2-way (e500v1)

4-way (e500v2)

256 (e500v1)

512 (e500v2)

Unified (I and D) tlbwe instruction

Loading...

Loading...