Register Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 2-57

2.15.6 User Local Control B Registers (UPMLCb0–UPMLCb3)

The contents of PMLCb0–PMLCb3 are reflected to UPMLCb0–UPMLCb3, which are read by

user-level software with mfpmr using the PMR numbers in Table 2-37.

2.15.7 Performance Monitor Counter Registers (PMC0–PMC3)

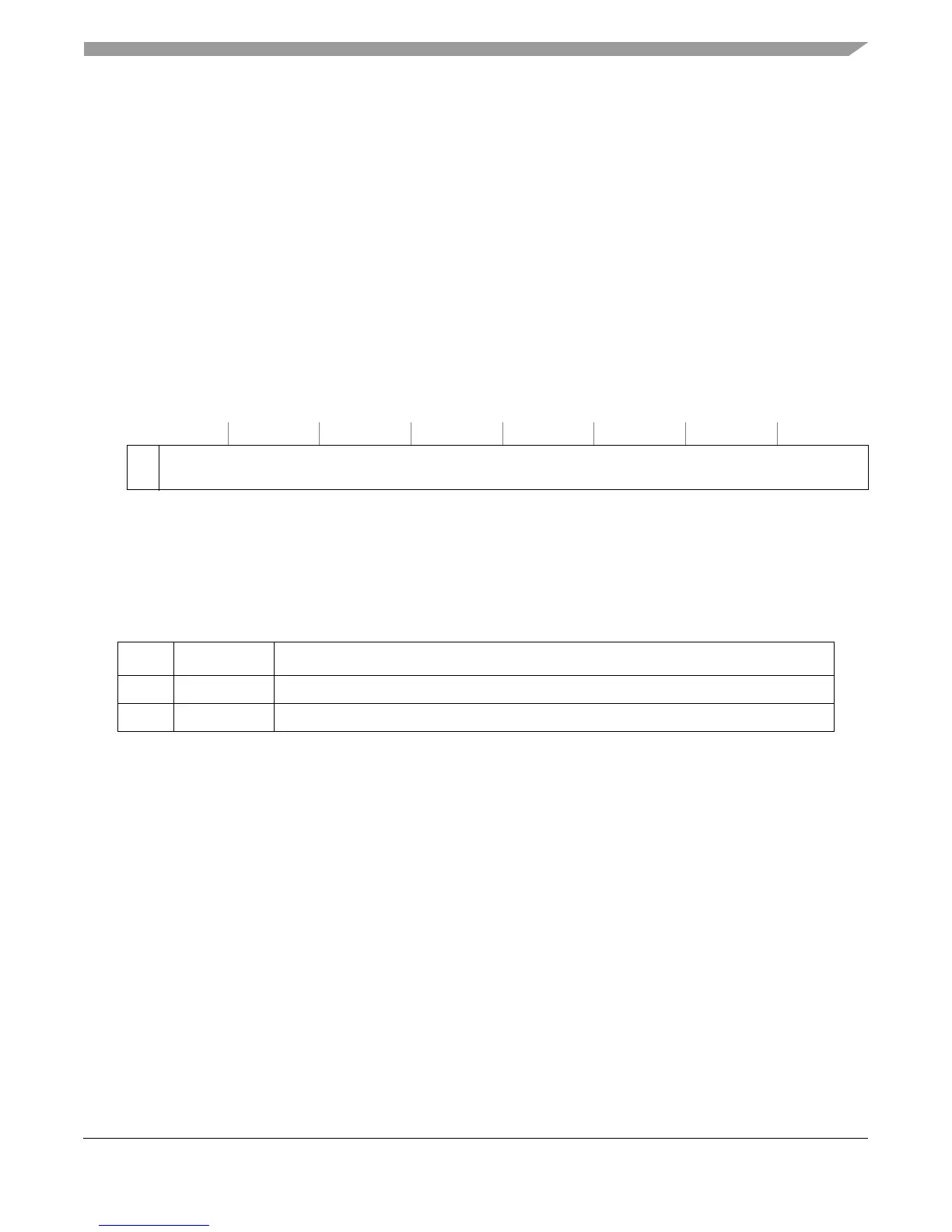

The performance monitor counter registers PMC0–PMC3, shown in Figure 2-42, are 32-bit

counters that can be programmed to generate interrupt signals when they overflow. Each counter

is enabled to count 128 events.

Table 2-41 describes the PMC register fields.

Counters overflow when the high-order bit (the sign bit) becomes set; that is, they reach the value

2,147,483,648 (0x8000_0000). However, an exception is not signaled unless PMGC0[PMIE] and

PMLCan[CE] are also set as appropriate.

The interrupts are masked by clearing MSR[EE]. An interrupt that is signaled while MSR[EE] is

zero is not taken until MSR[EE] is set. Setting PMGC0[FCECE] forces counters to stop counting

when an enabled condition or event occurs.

Software is expected to use mtpmr to explicitly set PMCs to non-overflowed values. Setting an

overflowed value may cause an erroneous exception. For example, if both PMGC0[PMIE] and

PMLCan[CE] are set and the mtpmr loads an overflowed value into PMCx, an interrupt may be

generated without an event counting having taken place.

PMC registers are accessed with mtpmr and mfpmr using the PMR numbers in Table 2-36.

PMC0 (PMR16)

PMC1 (PMR17)

PMC2 (PMR18)

PMC3 (PMR19)

UPMC0 (PMR0)

UPMC1 (PMR1)

UPMC2 (PMR2)

UPMC3 (PMR3)

Access: PMC0–PMC3: Supervisor-only

UPMC0–UPMC3: Supervisor/user read-only

32 33 63

R

OV Counter value

W

Reset All zeros

Figure 2-42. Performance Monitor Counter Registers (PMC0–PMC3)/

User Performance Monitor Counter Registers (UPMC0–UPMC3)

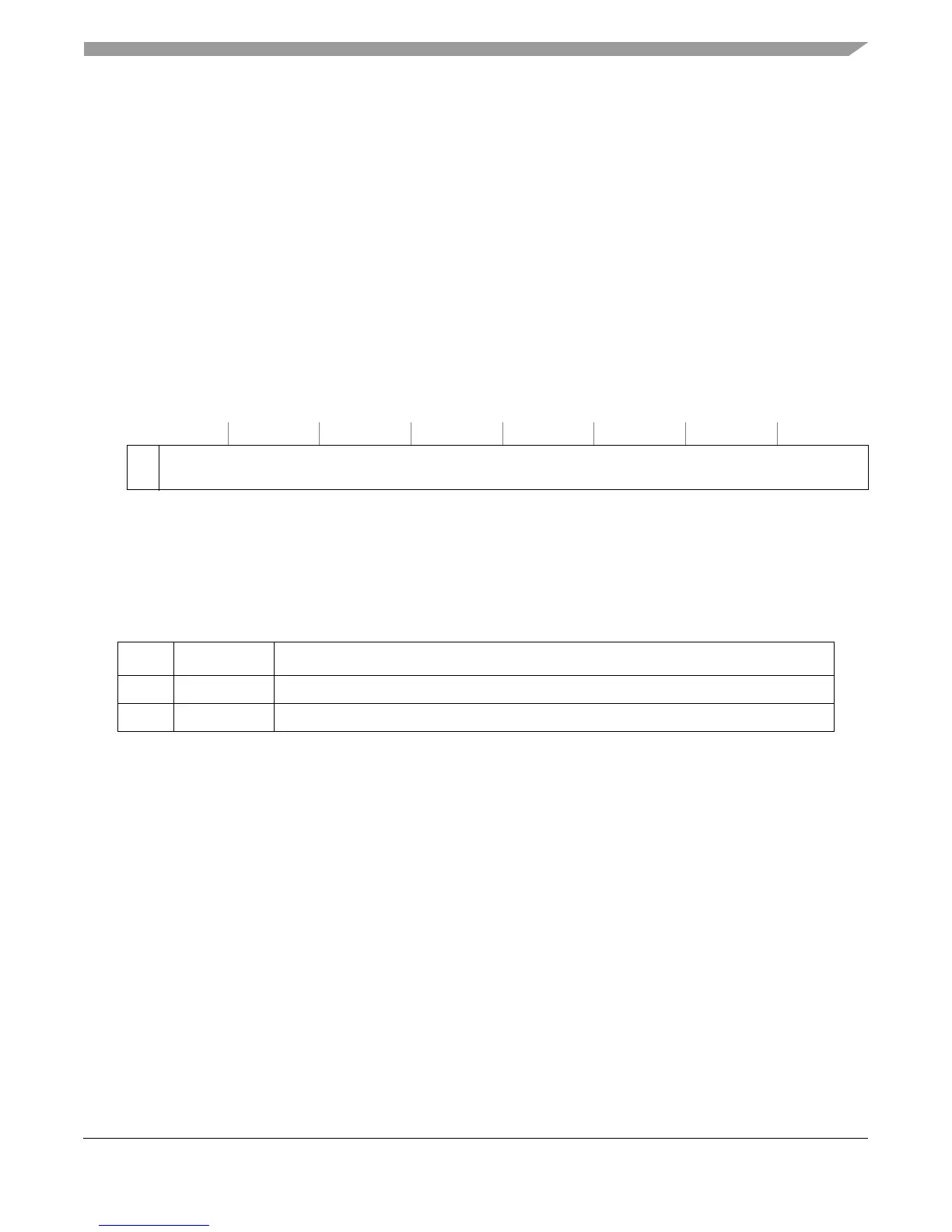

Table 2-41. PMC0–PMC3 Field Descriptions

Bits Name Description

32 OV Overflow. When this bit is set, it indicates this counter reaches its maximum value.

33–63 Counter Value Indicates the number of occurrences of the specified event.

Loading...

Loading...