Register Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 2-23

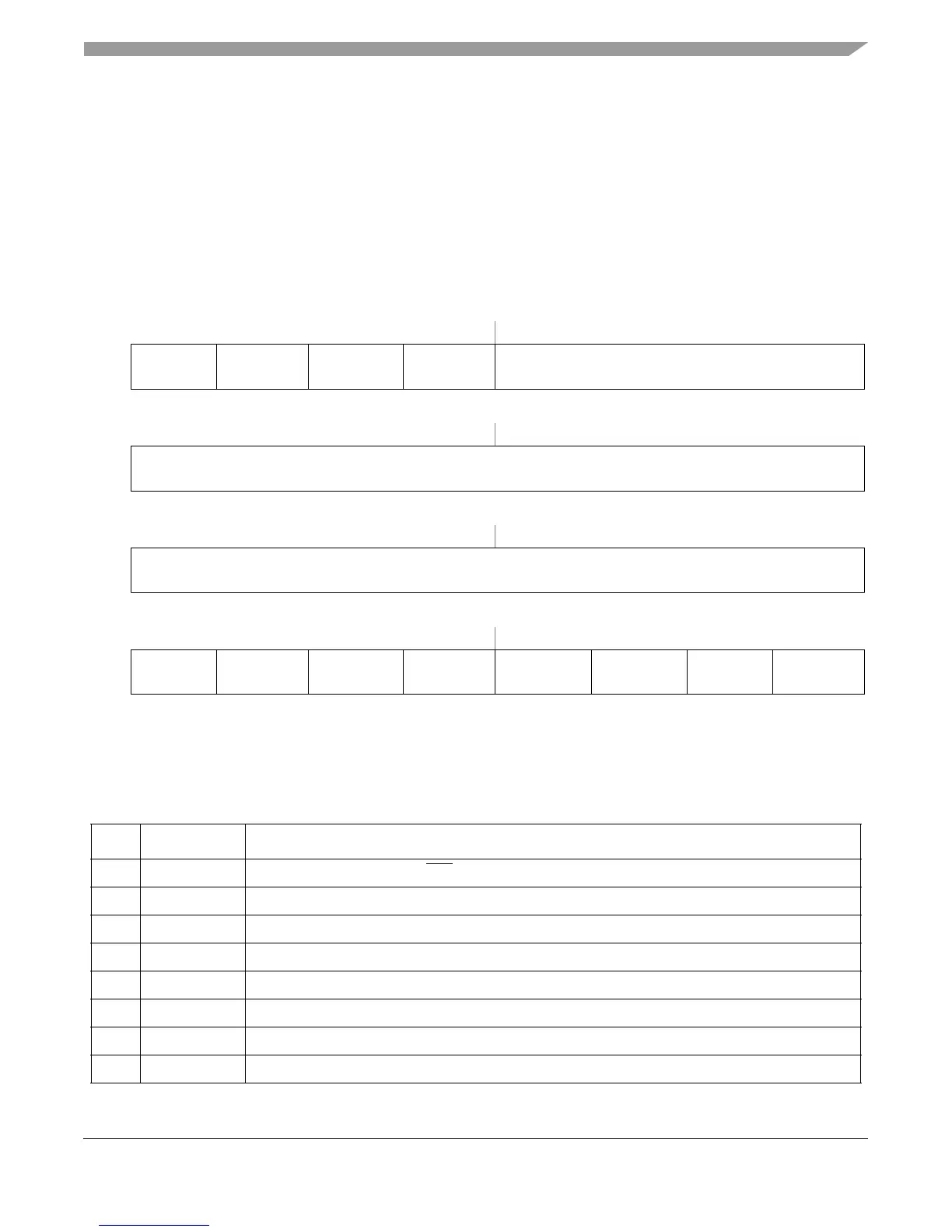

2.7.2.4 Machine Check Syndrome Register (MCSR)

When the core complex takes a machine check interrupt, it updates MCSR to differentiate between

machine check conditions. The MCSR indicates whether a machine check condition is

recoverable. When a condition bit is set, the core complex asserts MCP_OUT for system

information. ABIST status is logged in MCSR[48–54]. These bits do not initiate machine check

(or any other exception). An ABIST bit being set indicates an error being detected in the

corresponding module. The MCSR is shown in Figure 2-14.

Table 2-10 describes the MCSR fields.

SPR 572 Access: Supervisor-only

32 33 34 35 36 39

R

MCP ICPERR DCP_PERR DCPERR —

W

Reset All zeros

40 47

R

—

W

Reset All zeros

48 55

R

—

W

Reset All zeros

56 57 58 59 60 61 62 63

R

BUS_IAERR BUS_RAERR BUS_WAERR BUS_IBERR BUS_RBERR BUS_WBERR BUS_IPERR BUS_RPERR

W

Reset All zeros

Figure 2-14. Machine Check Syndrome Register (MCSR)

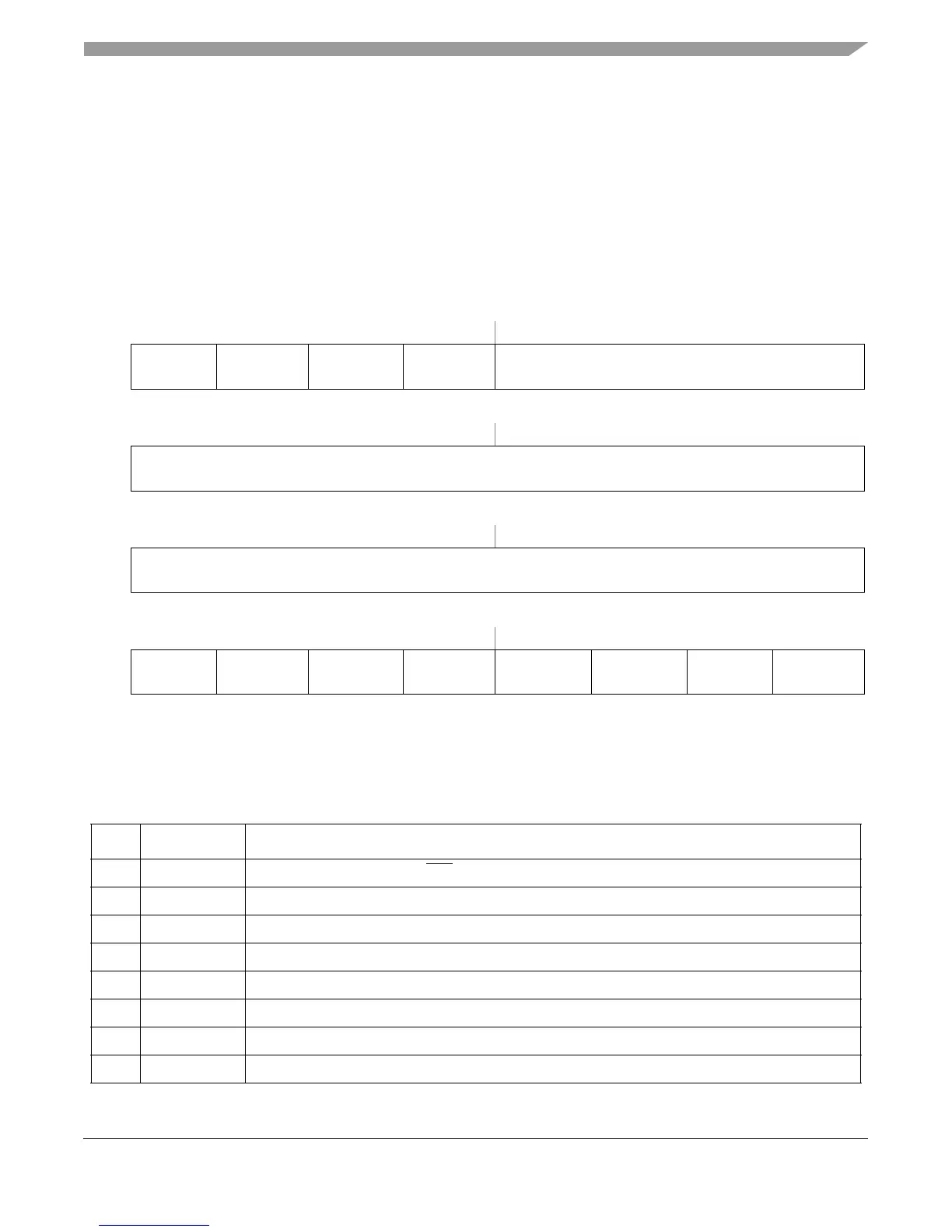

Table 2-10. MCSR Field Descriptions

Bit Name Description

32 MCP Machine check input to core

mcp

33 ICPERR Instruction cache parity error

34 DCP_PERR Data cache push parity error

35 DCPERR Data cache parity error

36–55 — Reserved, should be cleared.

56 BUS_IAERR Bus instruction address error

57 BUS_RAERR Bus read address error

58 BUS_WAERR Bus write address error

Loading...

Loading...