PowerPC e500 Core Family Reference Manual, Rev. 1

3-22 Freescale Semiconductor

Instruction Model

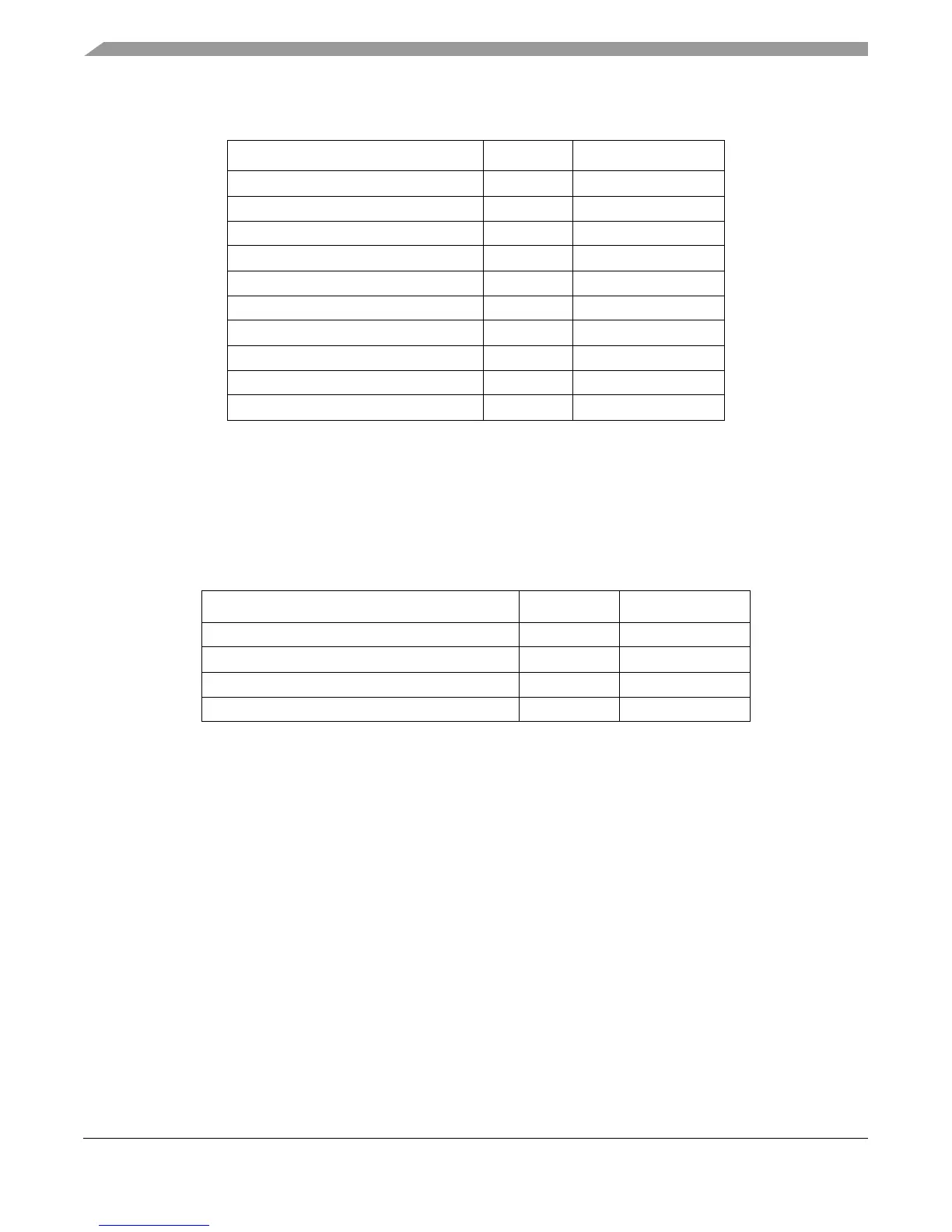

3.3.1.2.5 Integer Load and Store with Byte-Reverse Instructions

Table 3-13 describes integer load and store with byte-reverse instructions. These books were

defined in part to support the original PowerPC definition of little-endian byte ordering. Note that

Book E supports true little endian on a per-page basis.

3.3.1.2.6 Integer Load and Store Multiple Instructions

The load/store multiple instructions are used to move blocks of data to and from the GPRs. The

load multiple and store multiple instructions can have operands that require memory accesses

crossing a 4-Kbyte page boundary. As a result, these instructions can be interrupted by a data

storage interrupt associated with the address translation of the second page. Note that if one of

these instructions is interrupted, it may be restarted, requiring multiple memory accesses.

The Book E architecture defines the Load Multiple Word (lmw) instruction with rA in the range

of registers to be loaded as an invalid form. Load and store multiple accesses must be word

aligned; otherwise, they cause an alignment exception.

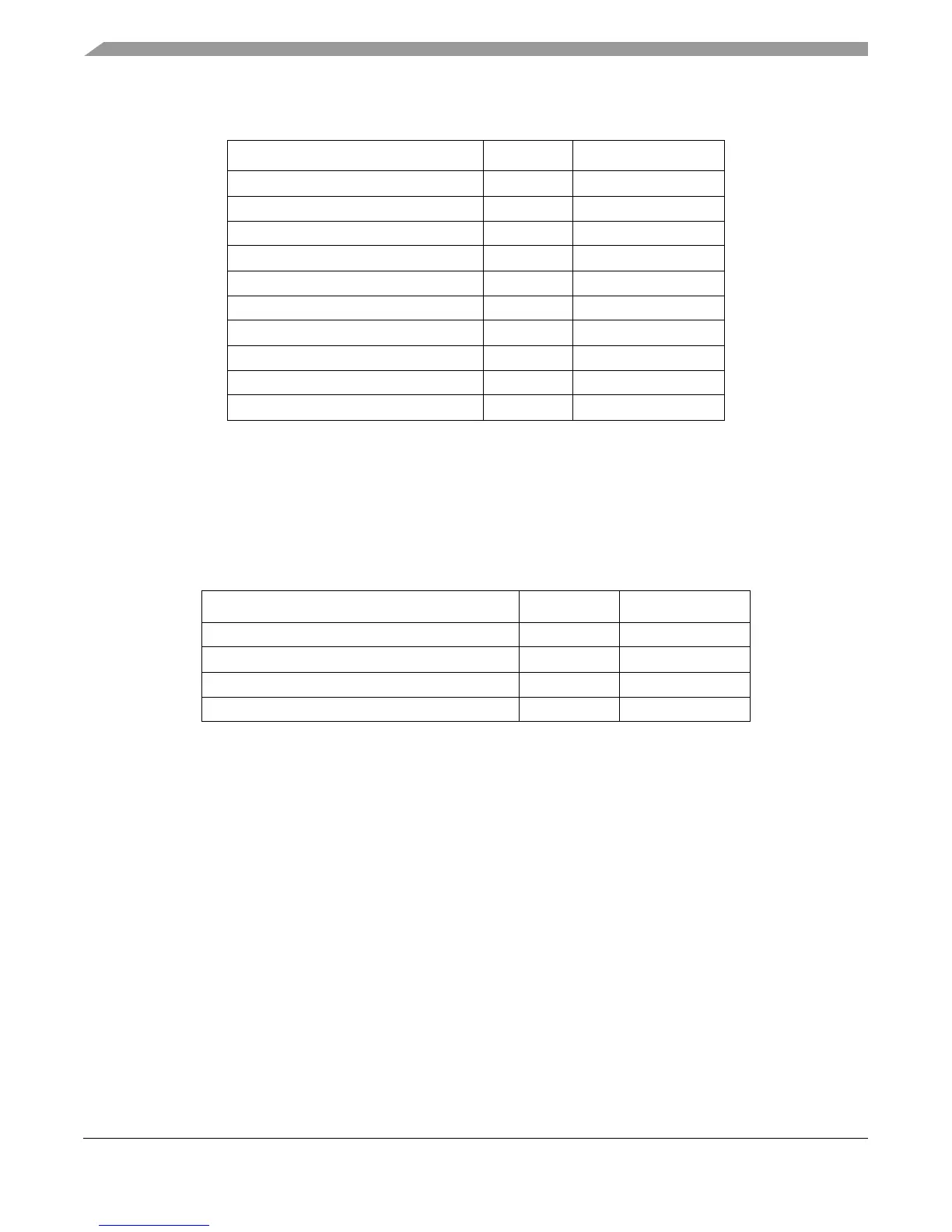

Store Byte with Update stbu rS,d(rA)

Store Byte with Update Indexed stbux rS,rA,rB

Store Half Word sth rS,d(rA)

Store Half Word Indexed sthx rS,rA,rB

Store Half Word with Update sthu rS,d(rA)

Store Half Word with Update Indexed sthux rS,rA,rB

Store Word stw rS,d(rA)

Store Word Indexed stwx rS,rA,rB

Store Word with Update stwu rS,d(rA)

Store Word with Update Indexed stwux rS,rA,rB

Table 3-13. Integer Load and Store with Byte-Reverse Instructions

Name Mnemonic Syntax

Load Half Word Byte-Reverse Indexed lhbrx rD,rA,rB

Load Word Byte-Reverse Indexed lwbrx rD,rA,rB

Store Half Word Byte-Reverse Indexed sthbrx rS,rA,rB

Store Word Byte-Reverse Indexed stwbrx rS,rA,rB

Table 3-12. Integer Store Instructions (continued)

Name Mnemonic Syntax

Loading...

Loading...