PowerPC e500 Core Family Reference Manual, Rev. 1

2-20 Freescale Semiconductor

Register Model

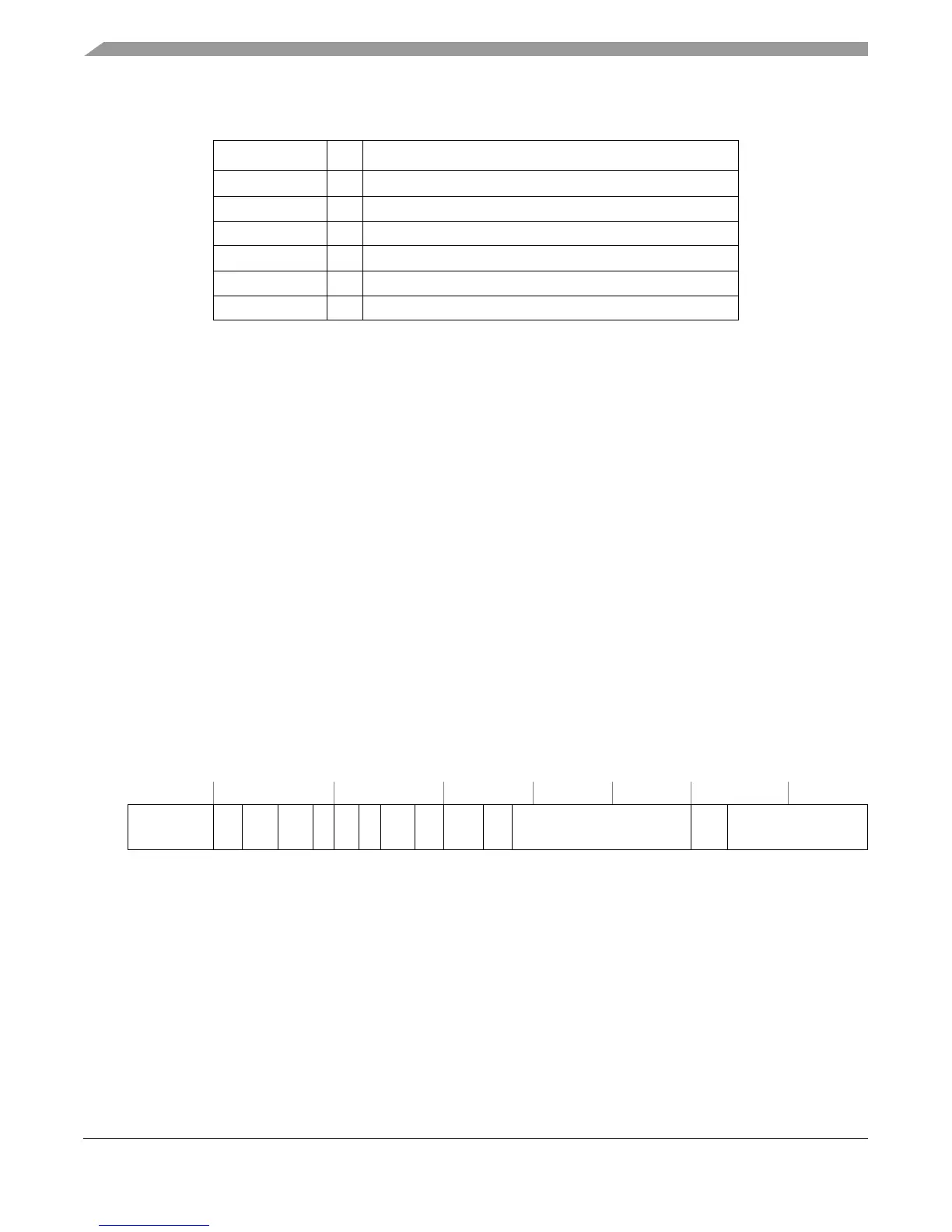

2.7.1.6 Exception Syndrome Register (ESR)

Figure 2-10 shows the ESR as it is defined on the e500.

The ESR provides a way to differentiate among exceptions that can generate an interrupt type.

When an interrupt is generated, bits corresponding to the specific exception that generated the

interrupt are set and all other ESR bits are cleared. Other interrupt types do not affect ESR

contents. The ESR does not need to be cleared by software. Table 2-9 shows ESR bit definitions.

The e500 defines ESR[SPE] as the SPE/embedded floating-point exception bit. It is set whenever

the processor takes an exception related to the execution of SPE or SPFP instructions. Note that

the e500 does not use the ESR for machine check interrupts, but instead uses the machine check

syndrome register, MCSR, described in Section 2.7.2.4, “Machine Check Syndrome Register

(MCSR).” The ESR is defined in Book E but differs in the following respects:

• The e500 defines ESR[DLK0] (bit 42) as ESR[DLK].

• The e500 defines ESR[DLK1] (bit 43) as ESR[ILK].

• The e500 defines ESR[SPE] (bit 56).

• The e500 does not implement FP, AP, PIE, or PUO.

IVOR16–IVOR31 — Reserved for future architectural use

IVOR32 528 (e500-specific) SPE APU unavailable

IVOR33 529 (e500-specific) Embedded floating-point data exception

IVOR34 530 (e500-specific) Embedded floating-point round exception

IVOR35 531 (e500-specific) Performance monitor

IVOR36–IVOR63 — Allocated for implementation-dependent use

SPR 62 Access: Supervisor-only

32 35 36 37 38 39 40 41 42 43 44 45 46 47 55 56 57 63

R

— PIL PPR PTR — ST — DLK ILK — BO — SPE —

W

Reset All zeros

Figure 2-10. Exception Syndrome Register (ESR)

Table 2-8. IVOR Assignments (continued)

IVOR Number SPR Interrupt Type

Loading...

Loading...