Register Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 2-21

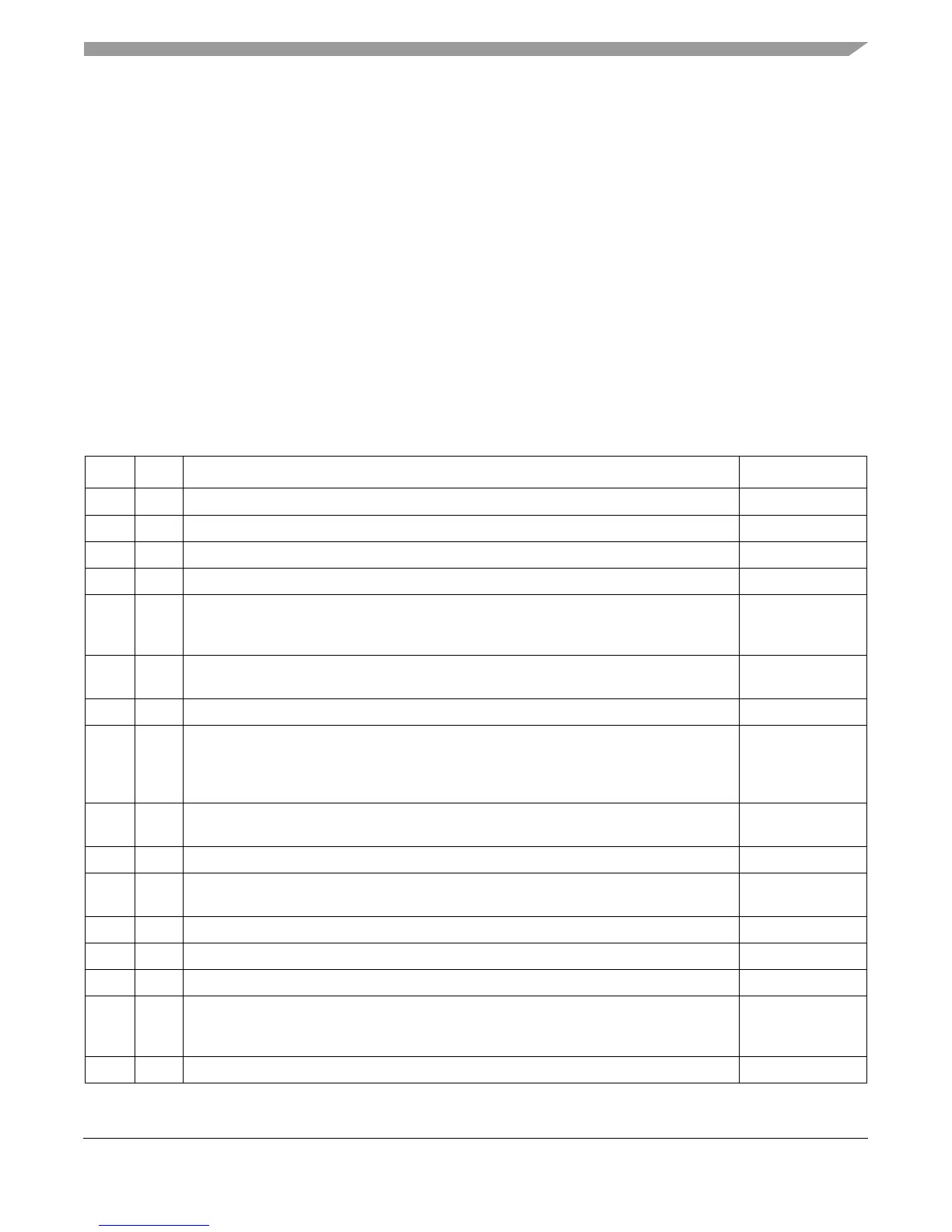

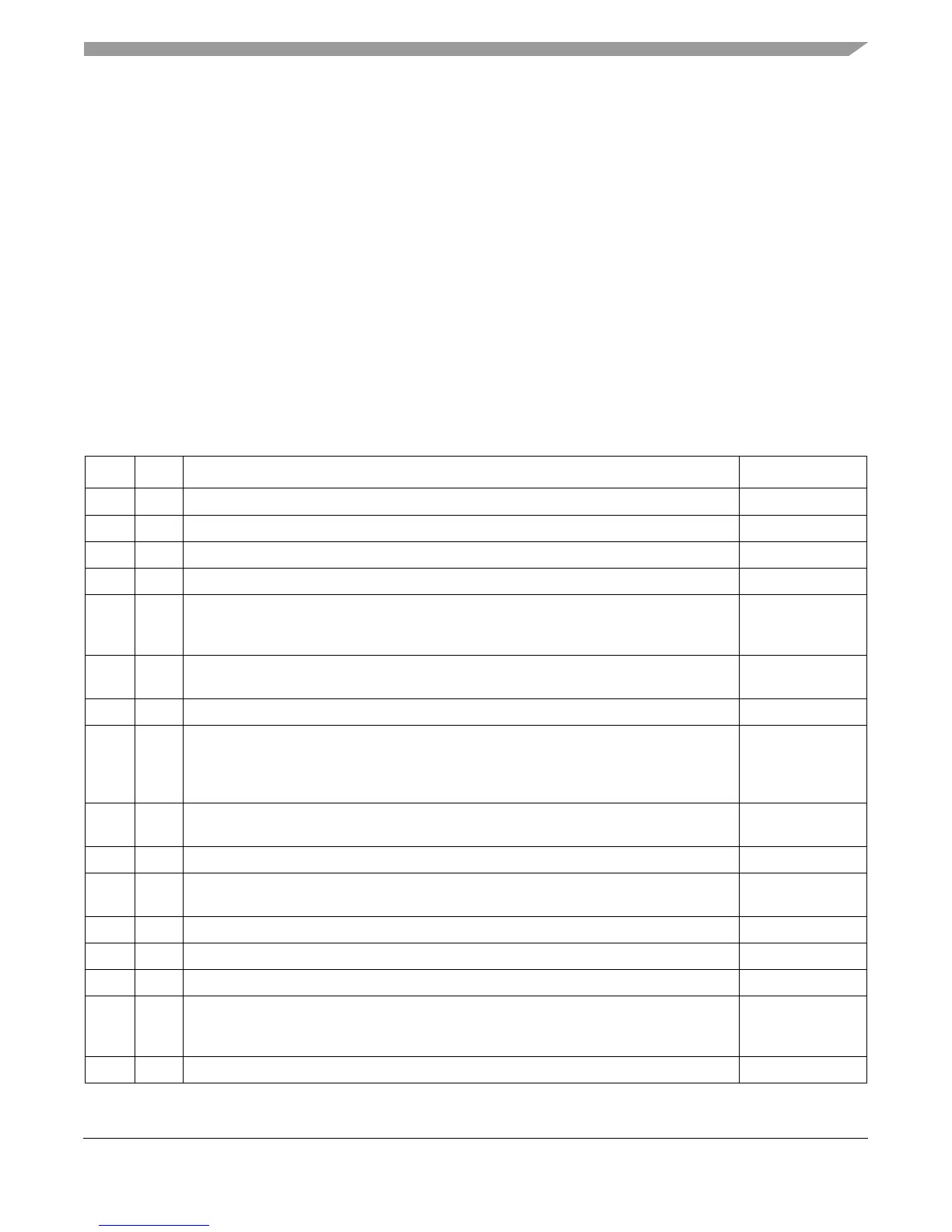

Table 2-9 describes the ESR fields, showing the associated interrupts. Note that an implementation

may implement additional ESR bits to identify implementation-specific or architected interrupt

types.

NOTE

ESR information is incomplete, so system software may need to

identify the type of instruction that caused the interrupt, examine the

TLB entry, and examine the ESR to fully identify the exception or

exceptions. For example, a data storage interrupt may be caused by

both a protection violation exception and a byte-ordering exception.

System software would have to look beyond ESR[BO], such as the

state of MSR[PR] in SRR1 and the TLB entry page protection bits to

determine if a protection violation also occurred.

Table 2-9. ESR Field Descriptions

Bits Name Syndrome Interrupt Types

32–35 — Reserved, should be cleared. (Defined by Book E as allocated.) —

36 PIL Illegal instruction exception Program

37 PPR Privileged instruction exception Program

38 PTR Trap exception Program

39 — Not supported on the e500. Defined by Book E as FP (floating-point operations). On the

e500, this bit is reserved and permanently cleared, indicating that the e500 does not

implement a Book E FPU. Setting it has no effect.

—

40 ST Store operation Alignment, DSI,

DTLB error

41 — Reserved, should be cleared. —

42 DLK Data cache locking (defined by Book E as DLK0). Settings are implementation dependent.

0 Default

1 On the e500, DLK is set when a DSI occurs because dcbtls, dcbtstls, or dcblc is

executed in user mode while MSR[UCLE] = 0.

DSI

43 ILK Instruction cache locking. (Book E defines this bit as DLK1.) Set when a DSI occurs

because icbtl or icblc is executed in user mode (MSR[PR] = 1 and MSR[UCLE] = 0)

DSI

44 — Not supported on the e500. Defined by Book E as AP (auxiliary processor operation). —

45 — Not supported on the e500. Unimplemented operation exception. On the e500,

unimplemented instructions are handled as illegal instructions.

Program

46 BO Byte-ordering exception DSI, ISI

47 — Not supported on the e500. Defined by Book E as PIE, Imprecise exception. —

48–55 — Reserved, should be cleared. —

56 SPE SPE/embedded floating-point exception bit (e500-specific)

0 Default

1 Any exception caused by an SPE or and SPFP instruction occurred.

57–63 — Reserved, should be cleared (defined by Book E as allocated). —

Loading...

Loading...