PowerPC e500 Core Family Reference Manual, Rev. 1

11-12 Freescale Semiconductor

L1 Caches

The instruction cache is loaded only as a result of instruction fetching or by an Instruction Cache

Block Touch and Lock Set (icbtls) instruction. It is not snooped for general coherency with other

caches; however, it is snooped when the Instruction Cache Block Invalidate (icbi) instruction is

executed by this processor or any other processor in the system. Instruction cache coherency must

be maintained by software and is supported by a fast hardware flash invalidation capability as

described in Section 11.5, “L1 Data Cache Flushing.” Also, the flushing of self-modifying code

from the data cache is described in Section 3.3.1.2.1, “Self-Modifying Code.”

11.3.3 Snoop Signaling

Cache coherency is maintained automatically by hardware through snooping the CCB. A bus

transaction is enabled for snooping by setting the coherency-required bit (M) in the TLBs

(WIMGE = 0bxx1xx). The M bit state is sent with the address on the internal global signal (gbl

).

If gbl

is asserted, the CCB transaction should be snooped by other bus masters.

To determine the action to take due to a snoop, the cache coherency protocol uses transfer type

(ttx) encodings, which are transmitted on the CCB with the address. See Section 13.2, “Signal

Summary.” These encodings indicate whether a transaction is a read or write and whether a

reading bus master has an intent to modify the cache line. The core complex uses these encodings

as a CCB master to signal its intent to other snooping caches.

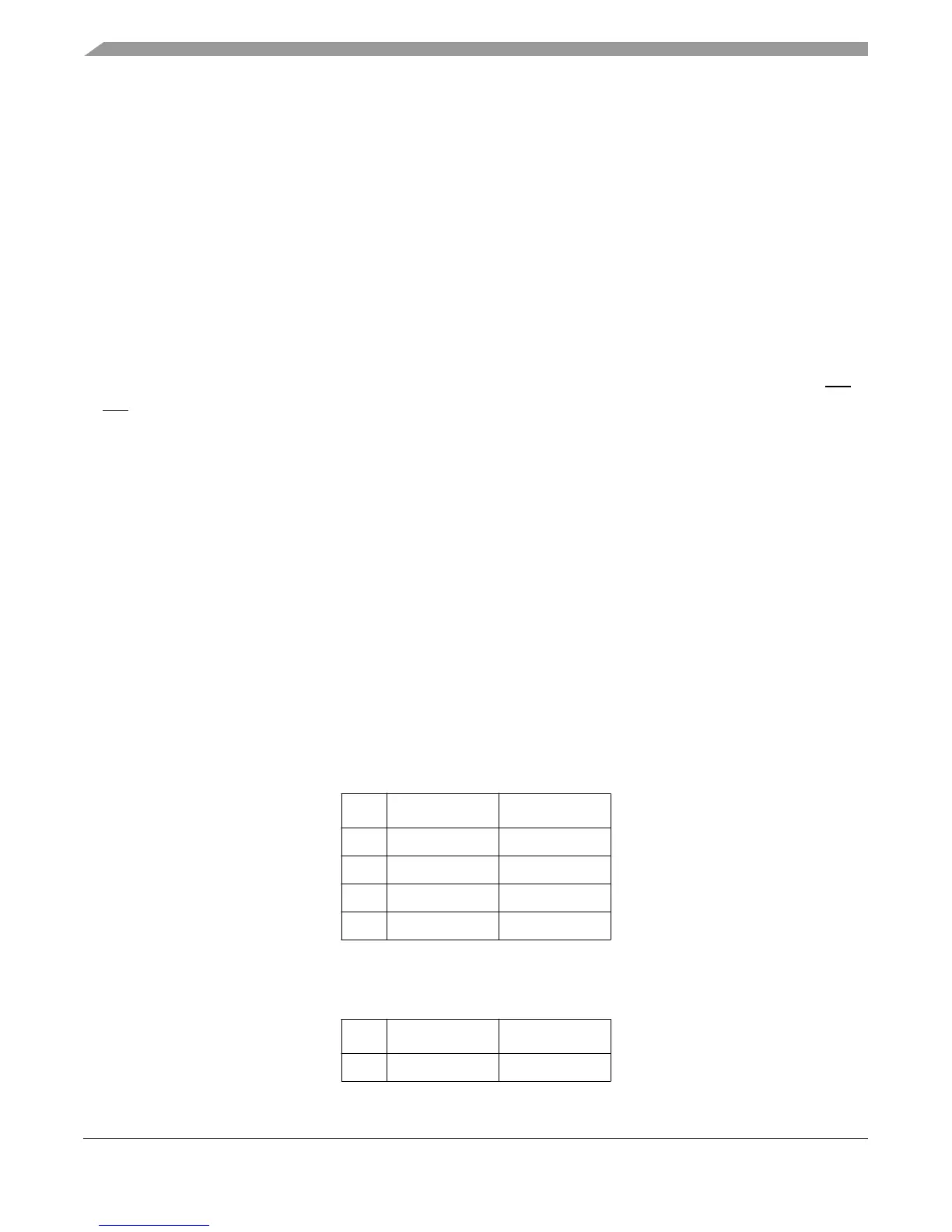

Clean, flush, and kill are three basic snoops that affect the L1 data cache. Table 11-4 describes the

state changes caused by these snoops.

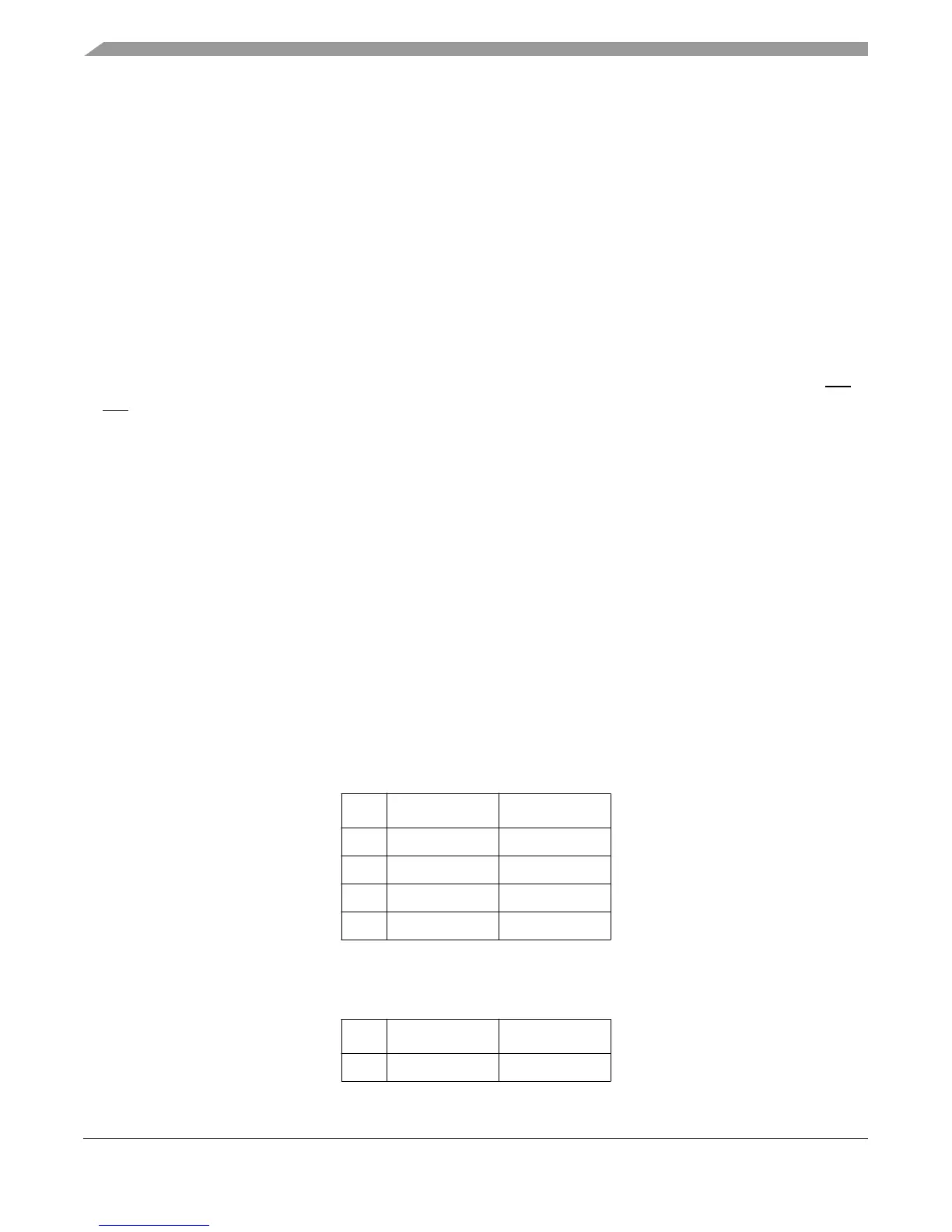

The instruction cache is not snooped, except in the case of the ikill, so coherency must be

maintained by software. However, the core complex does support a fast instruction cache

invalidation capability as described in Section 11.4.3, “L1 Instruction and Data Cache Flash

Invalidation.” Also, Section 3.3.1.2.1, “Self-Modifying Code,” describes flushing of

self-modifying code.

Table 11-5 describes state changes caused by the ikill snoop.

Table 11-4. Data Cache Snoop Coherency State Transitions

Event Initial State Final State

clean M, E, or S S

clean I I

flush Any I

kill Any I

Table 11-5. Instruction Cache Snoop Coherency State Transitions

Event Initial State Final State

ikill V or I I

Loading...

Loading...