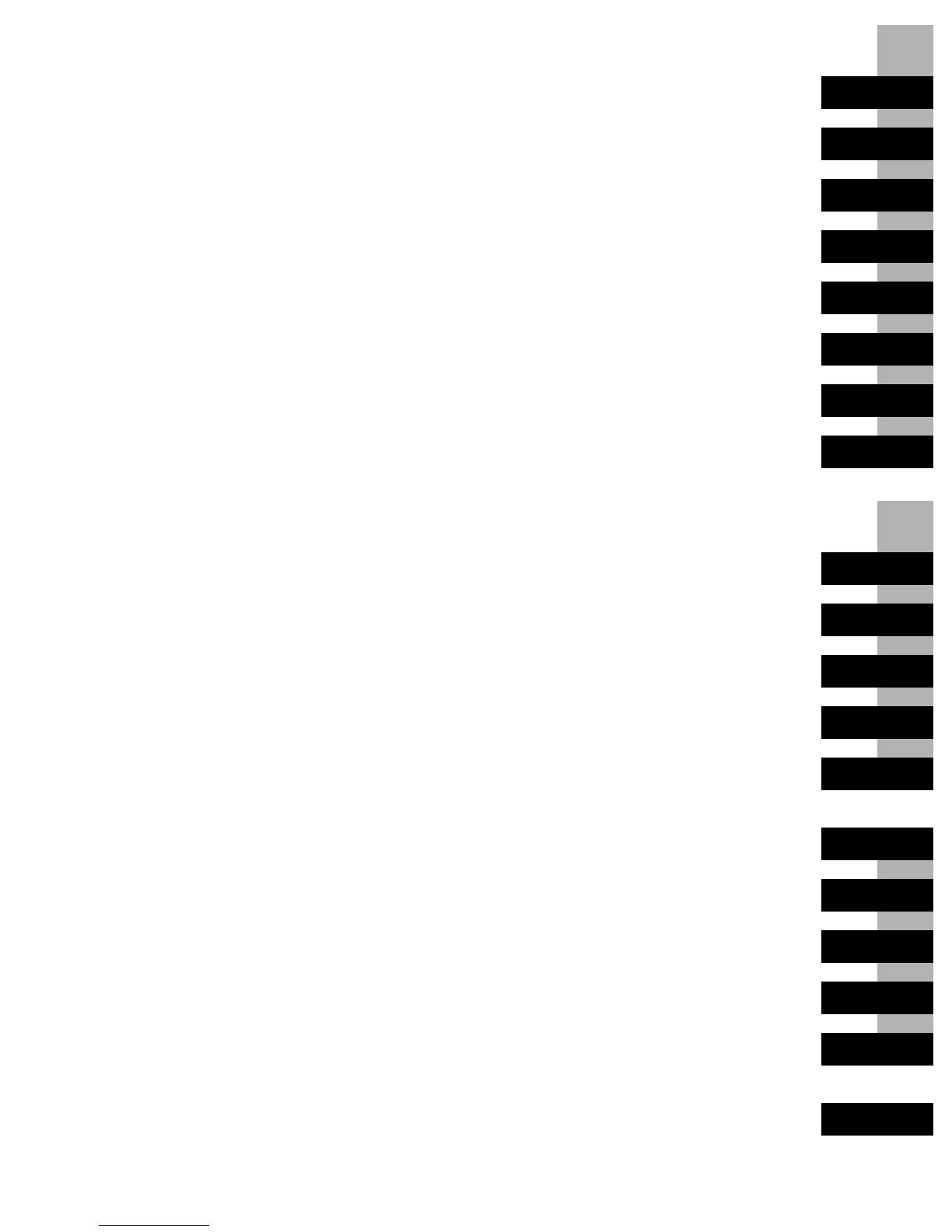

Part I—e500 Core I

Core Complex Overview 1

Register Model 2

Instruction Model 3

Execution Timing 4

Interrupts and Exceptions 5

Power Management 6

Performance Monitor 7

Debug Support 8

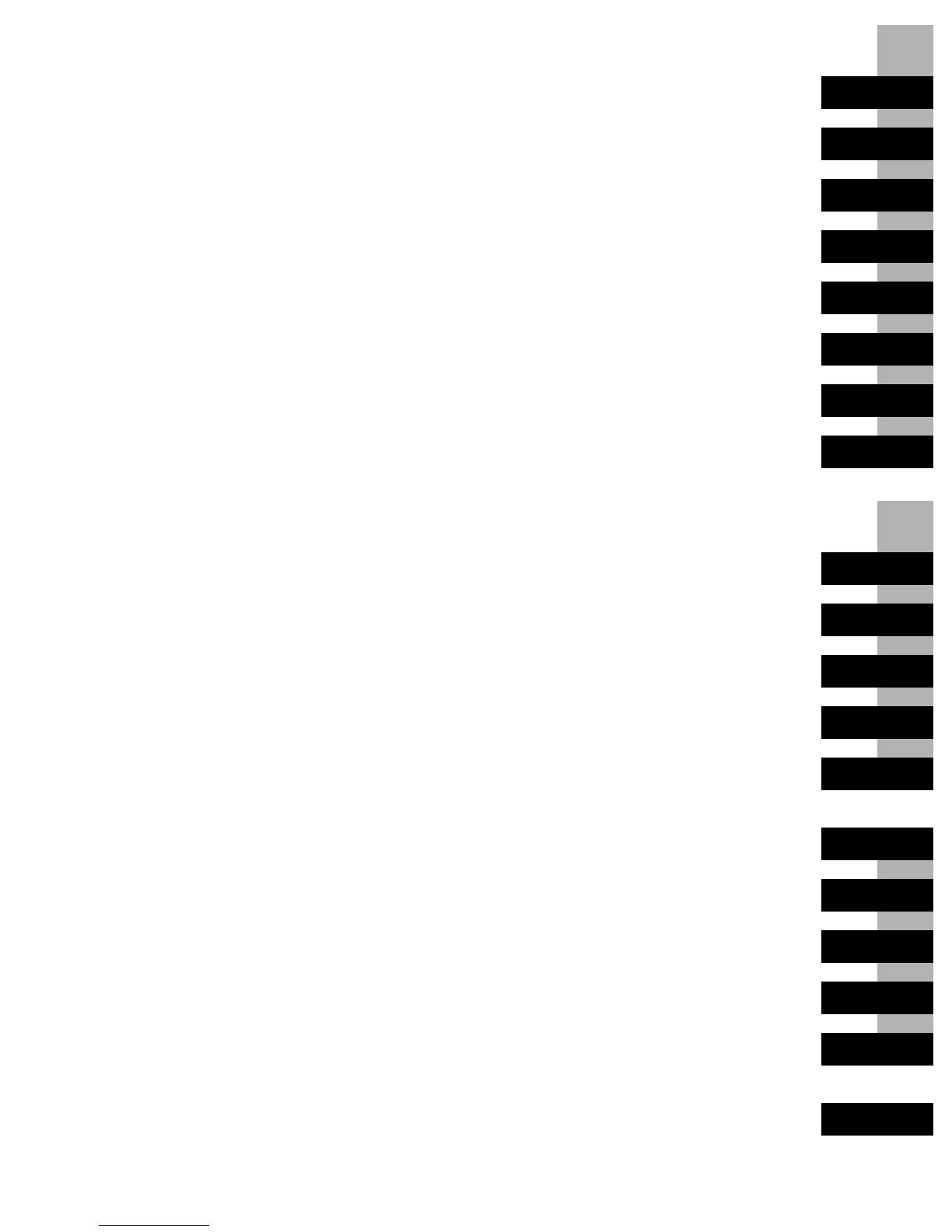

Part II—e500 Core Complex II

Timer Facilities 9

Auxiliary Processing Units (APUs) 10

L1 Caches 11

Memory Management Units 12

Core Complex Bus (CCB) 13

Appendix A—Programming Examples A

Appendix B—Guidelines for 32-Bit Book E B

Appendix C—Simplified Mnemonics for PowerPC Instructions C

Appendix D—Opcode Listings D

Appendix E—Revision History E

Index IND

Loading...

Loading...