PowerPC e500 Core Family Reference Manual, Rev. 1

10-2 Freescale Semiconductor

Auxiliary Processing Units (APUs)

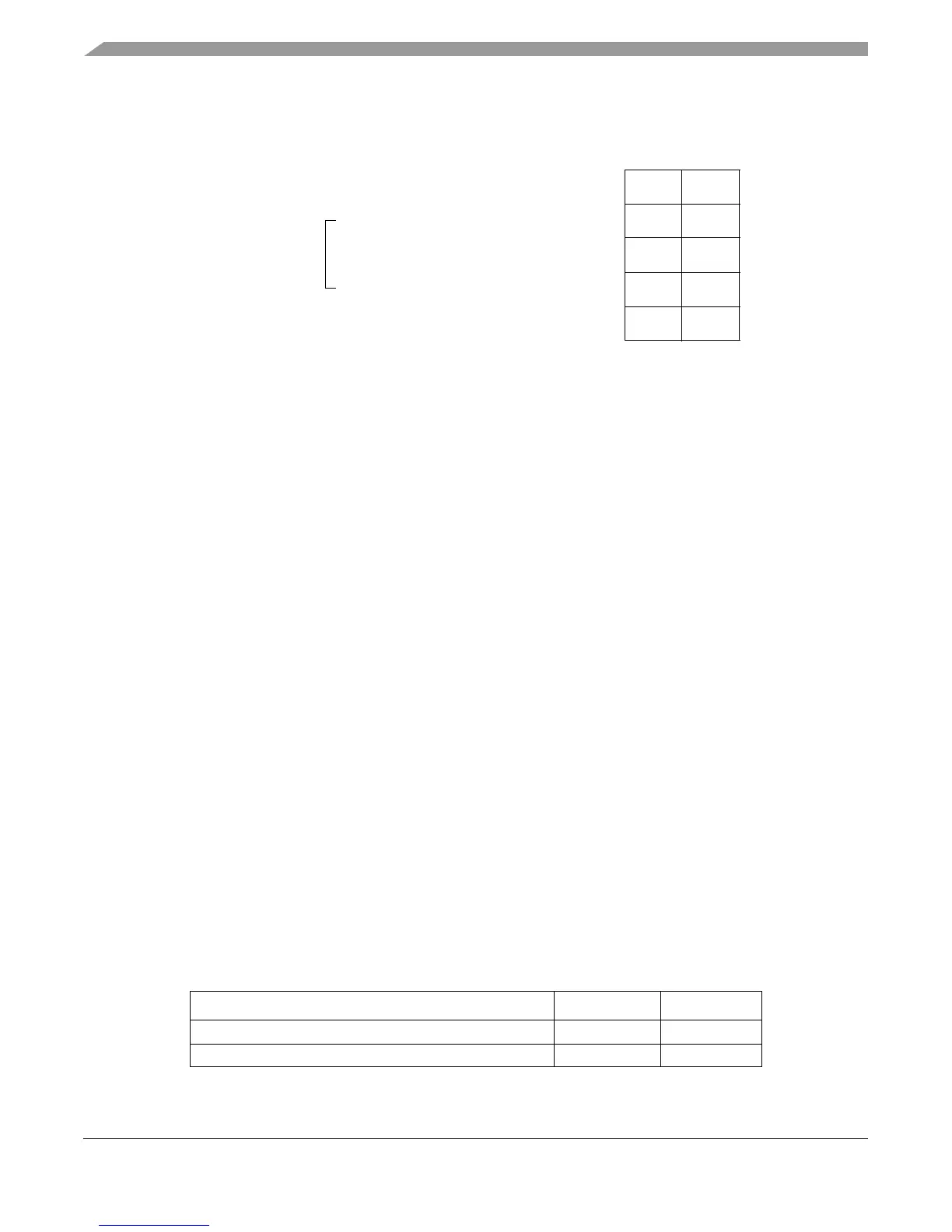

Note that the SPE APU and the two single-precision floating-point APUs were combined in the

original implementation of the e500v1, as shown in Figure 10-1.

The e500 also implements the branch target buffer (BTB) locking APU, which is not defined by

the EIS. See Section 10.2, “Branch Target Buffer (BTB) Locking APU.”

10.2 Branch Target Buffer (BTB) Locking APU

The core complex provides a 512-entry BTB for efficient processing of branch instructions. The

BTB is a branch target address cache, organized as 128 rows with four-way set associativity, that

holds the address and target instruction of the 512 most-recently taken branches, each with a 2-bit,

dynamically updated branch history table that indicates four levels of likelihood that the branch

will be taken (strongly taken, taken, not taken, strongly not taken). The BTB provides quick access

to branch targets and history bits that allow efficient branch prediction.

The core complex also provides support for locking and unlocking BTB entries for deterministic

branch behavior. In particular, the BTB locking APU gives the user the ability to lock, unlock, and

invalidate BTB entries.

10.2.1 BTB Locking APU Programming Model

The BTB locking APU defines additional instructions and register resources, which are described

in the following sections. It does not define additional interrupts.

10.2.1.1 BTB Locking APU Instructions

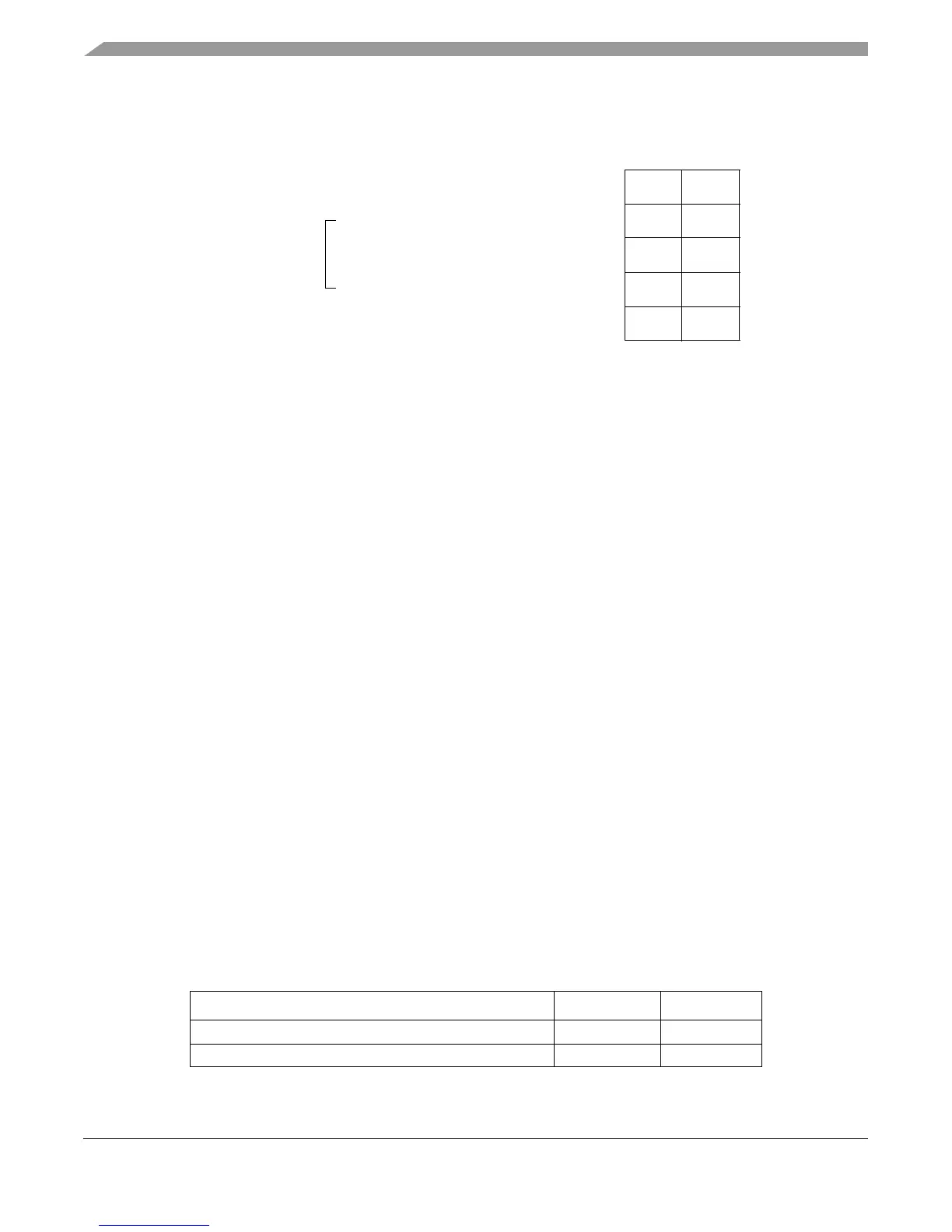

Table 10-1 lists the BTB locking instructions, which are described in detail in Section 3.9.1,

“Branch Target Buffer (BTB) Locking Instructions.”

Vector and Floating-Point APUs e500 v1 e500 v2

Original SPE

Definition

SPE vector instructions ev…

√√

Vector single-precision floating-point evfs…

√√

Scalar single-precision floating-point efs…

√√

Scalar double-precision floating-point efd…

√

Figure 10-1. Vector and Floating-Point APUs

Table 10-1. BTB Locking APU Instructions

Name Mnemonic Syntax

Branch Buffer Load Entry and Lock Set bblels —

Branch Buffer Entry Lock Reset bbelr —

Loading...

Loading...