PowerPC e500 Core Family Reference Manual, Rev. 1

5-26 Freescale Semiconductor

Interrupts and Exceptions

NOTE

To avoid redundant decrementer interrupts, before reenabling

MSR[EE], the interrupt handling routine must clear TSR[DIS] by

writing a word to TSR using mtspr with a 1 in any bit position to be

cleared and 0 in all others. The data written to the TSR is not direct

data, but a mask. Writing a 1 to this bit causes it to be cleared; writing

a 0 has no effect.

5.7.10 Fixed-Interval Timer Interrupt

A fixed-interval timer interrupt occurs when no higher priority exception exists, a fixed-interval

timer exception exists (TSR[FIS] = 1), and the interrupt is enabled (TCR[FIE] = 1 and

MSR[EE] = 1). The “Timers” chapter in the EREF describes Book E and EIS aspects of the

fixed-interval timer.

The fixed-interval timer period is determined by TCR[FP], which, when concatenated with

TCR[FPEXT], specifies one of 64 bit locations of the time base used to signal a fixed-interval

timer exception on a transition from 0 to 1.

TCR[FPEXT],TCR[FP] = 000000 selects TBU[32]. TCR[FPEXT],TCR[FP] = 111111 selects

TBL[63].

NOTE

MSR[EE] also enables external input and decrementer interrupts.

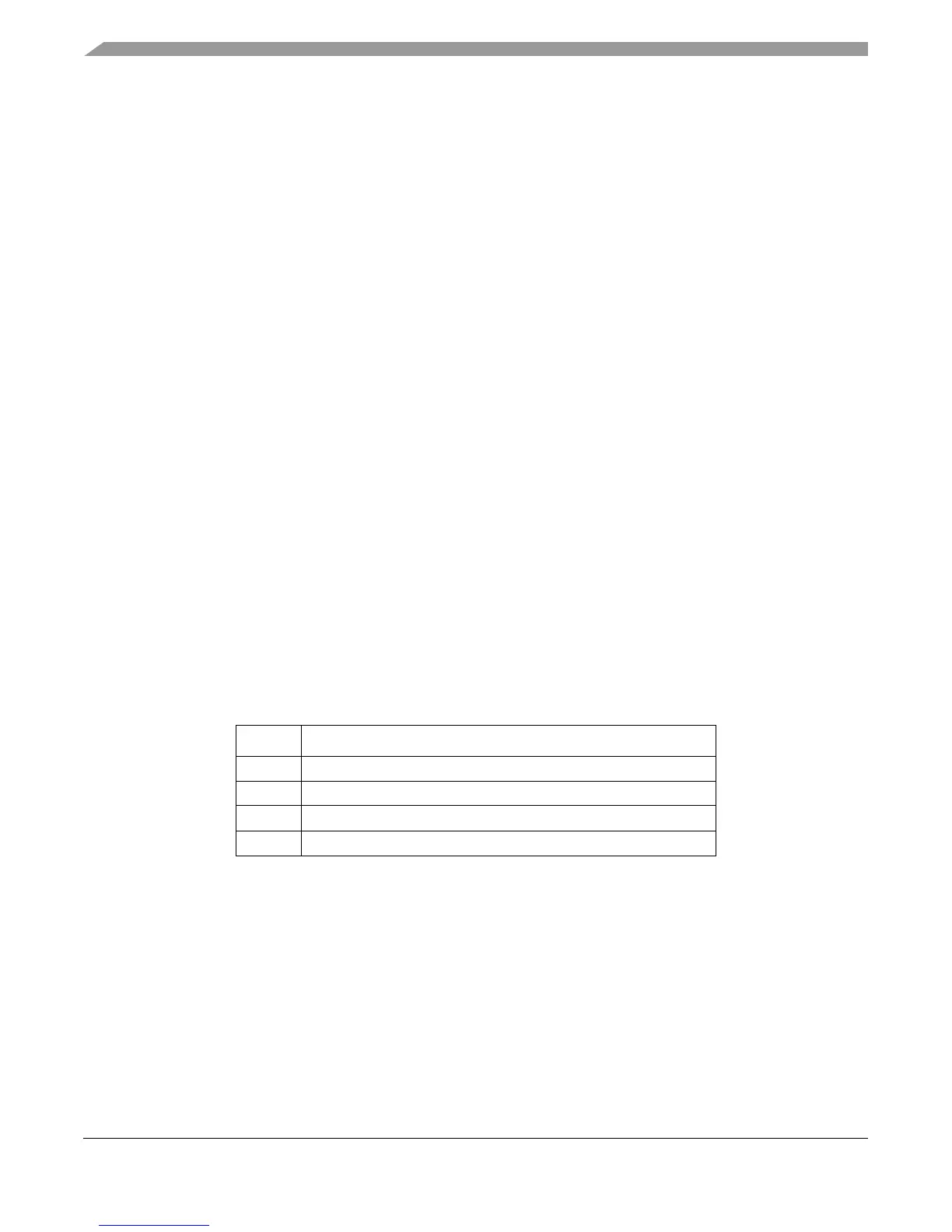

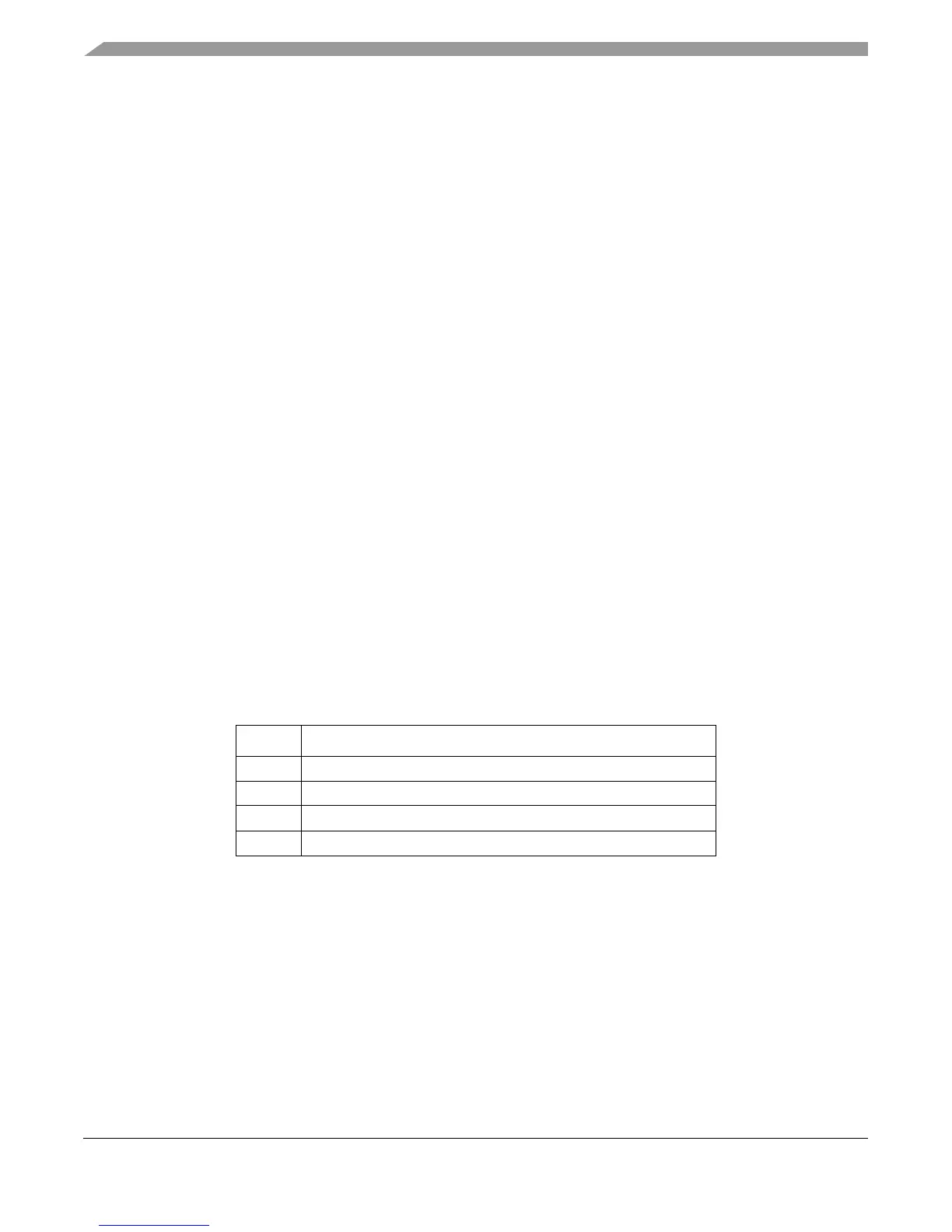

SRR0, SRR1, MSR, and TSR are updated as shown in Table 5-21.

Instruction execution resumes at address IVPR[32–47] || IVOR11[48–59] || 0b0000.

NOTE

To avoid redundant fixed-interval timer interrupts, before reenabling

MSR[EE], the interrupt handling routine must clear TSR[FIS] by

writing a word to TSR using mtspr with a 1 in any bit position to be

cleared and 0 in all others. The data written to the TSR is not direct

data, but a mask. Writing a 1 causes the bit to be cleared; writing a 0

has no effect.

Table 5-21. Fixed-Interval Timer Interrupt Register Settings

Register Setting

SRR0 Set to the effective address of the next instruction to be executed.

SRR1 Set to the MSR contents at the time of the interrupt.

MSR CE, ME, and DE are unchanged. All other MSR bits are cleared.

TSR FIS is set.

Loading...

Loading...