Instruction Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 3-19

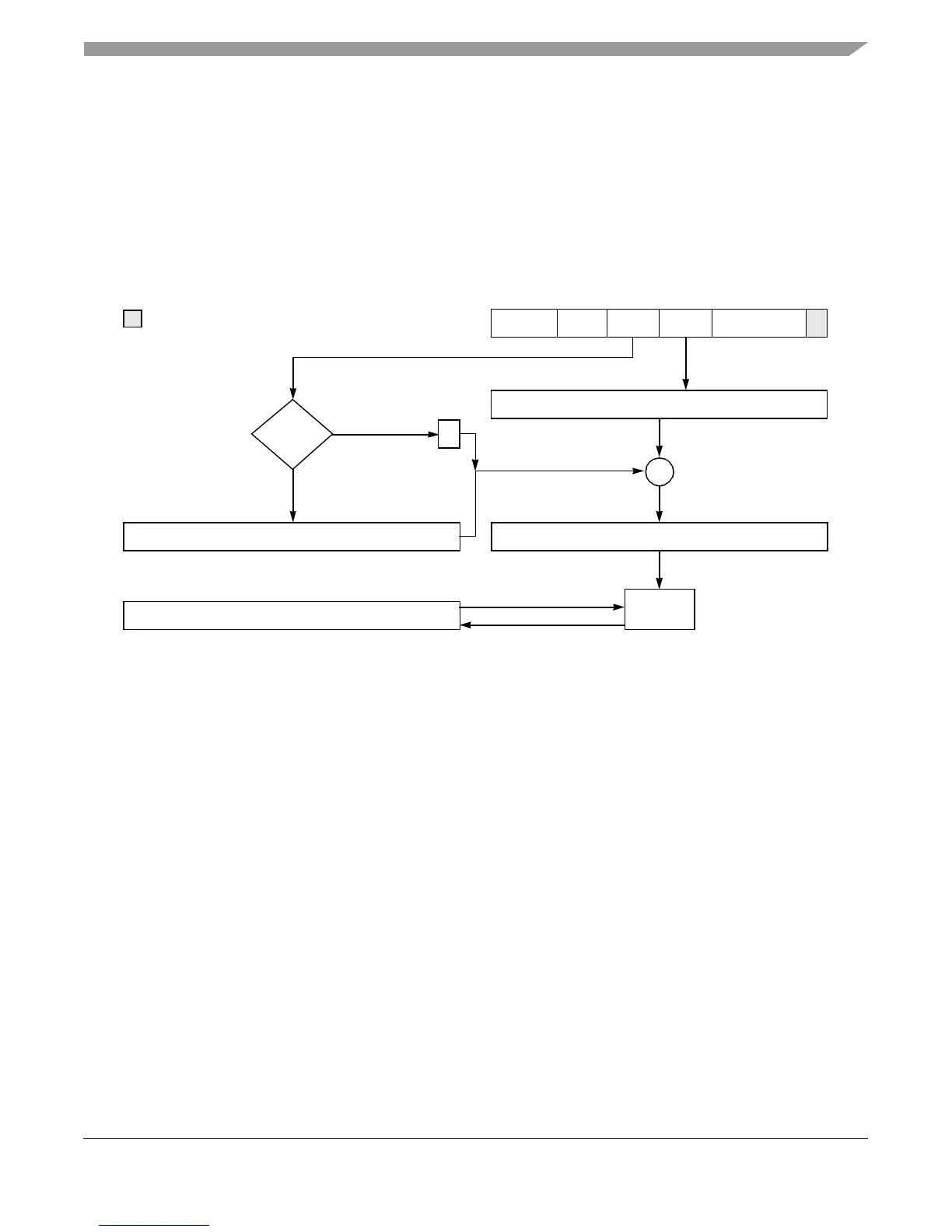

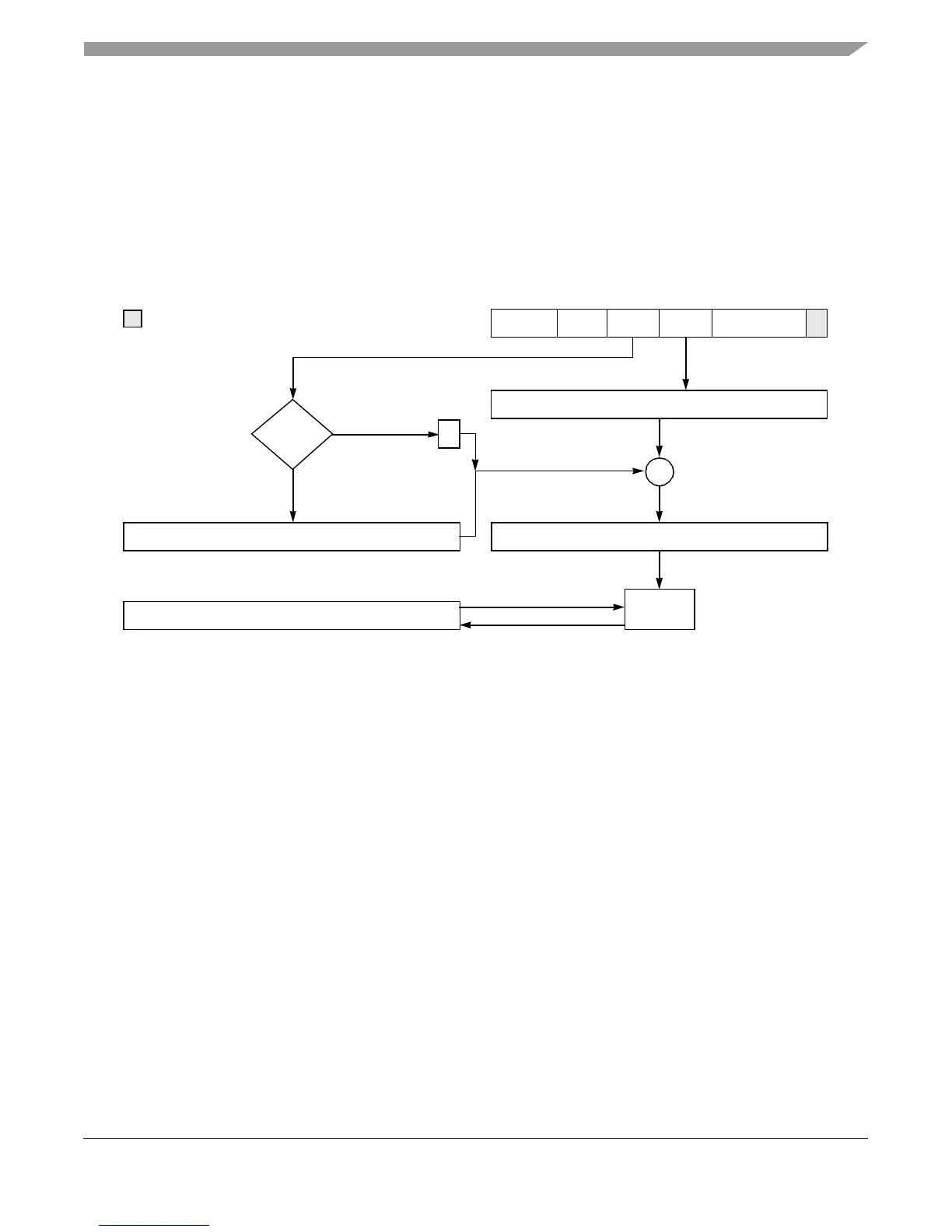

• Register indirect with index addressing for integer loads and stores. Instructions using this

addressing mode cause the contents of two general-purpose registers (specified as operands

rA and rB) to be added in the generation of the effective address. A zero in place of the rA

operand causes a zero to be added to the contents of the general-purpose register specified

in operand rB. The option to specify rA or 0 is shown in the instruction descriptions as

(rA|0).

Figure 3-2 shows how an effective address is generated using this addressing mode.

Figure 3-2. Register Indirect with Index Addressing for Integer Loads/Stores

• Register indirect addressing for integer loads and stores. Instructions using this addressing

mode use the contents of the GPR specified by the rA operand as the effective address. A

zero in the rA operand causes an effective address of zero to be generated. The option to

specify rA or 0 is shown in the instruction descriptions as (rA|0).

No

32 63

GPR (rA)

0

+

32 63

GPR (rD/rS)

Memory

Interface

Store

Load

Ye s

031

GPR (rB)

Instruction Encoding:

rA=0?

031

Effective Address

056101115162021 3031

Opcode rD/rS rA rB Subopcode 0

Reserved

Loading...

Loading...