Instruction Model

PowerPC e500 Core Family Reference Manual, Rev. 1

Freescale Semiconductor 3-15

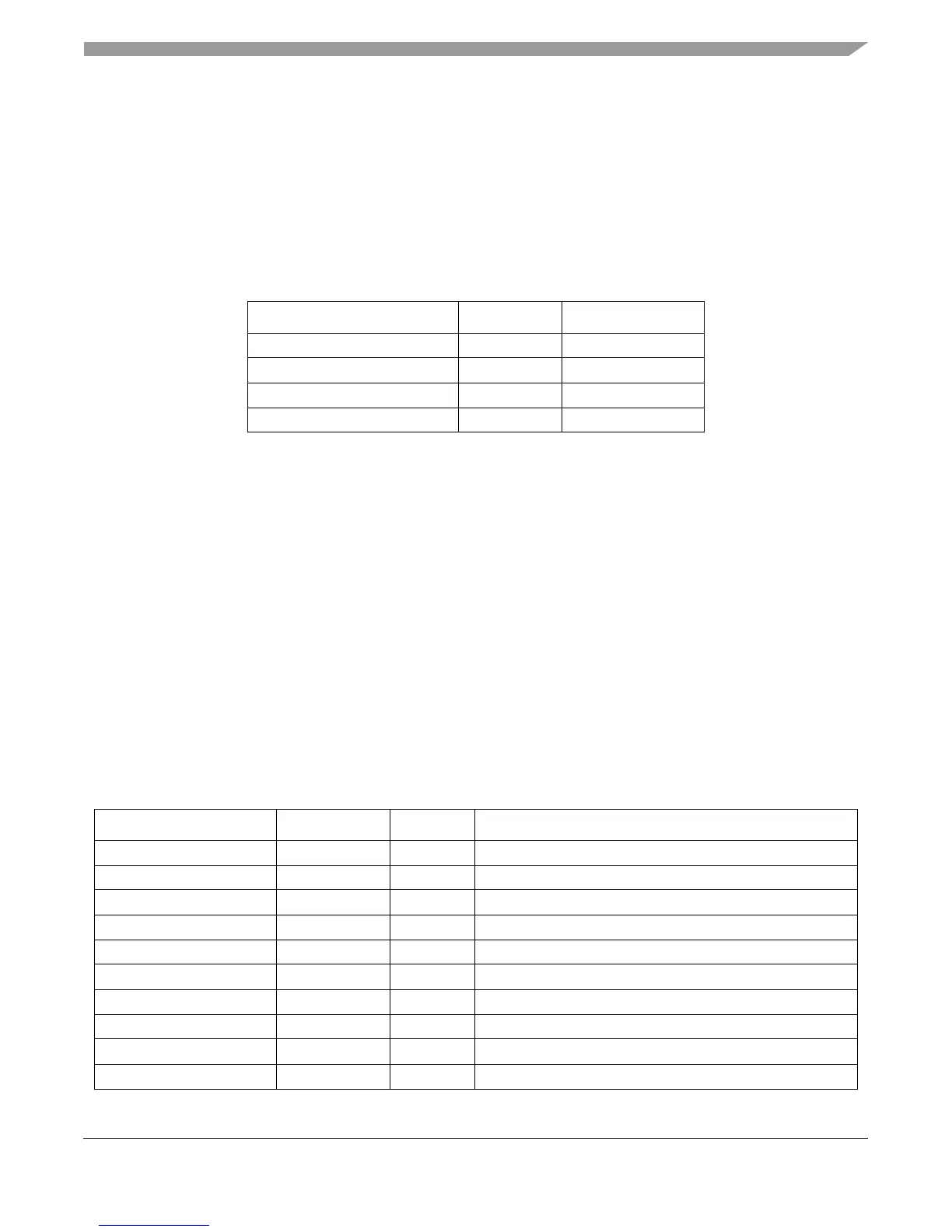

3.3.1.1.2 Integer Compare Instructions

The integer compare instructions algebraically or logically compare the contents of register rA

with either the zero-extended value of the UIMM operand, the sign-extended value of the SIMM

operand, or the contents of rB. The comparison is signed for cmpi and cmp and unsigned for

cmpli and cmpl. Table 3-7 lists integer compare instructions. Note that the L bit must be 0 for

32-bit implementations.

The crD operand can be omitted if the result of the comparison is to be placed in CR0. Otherwise

the target CR field must be specified in crD by using an explicit field number.

For information on simplified mnemonics for the integer compare instructions see Appendix C,

“Simplified Mnemonics for PowerPC Instructions.”

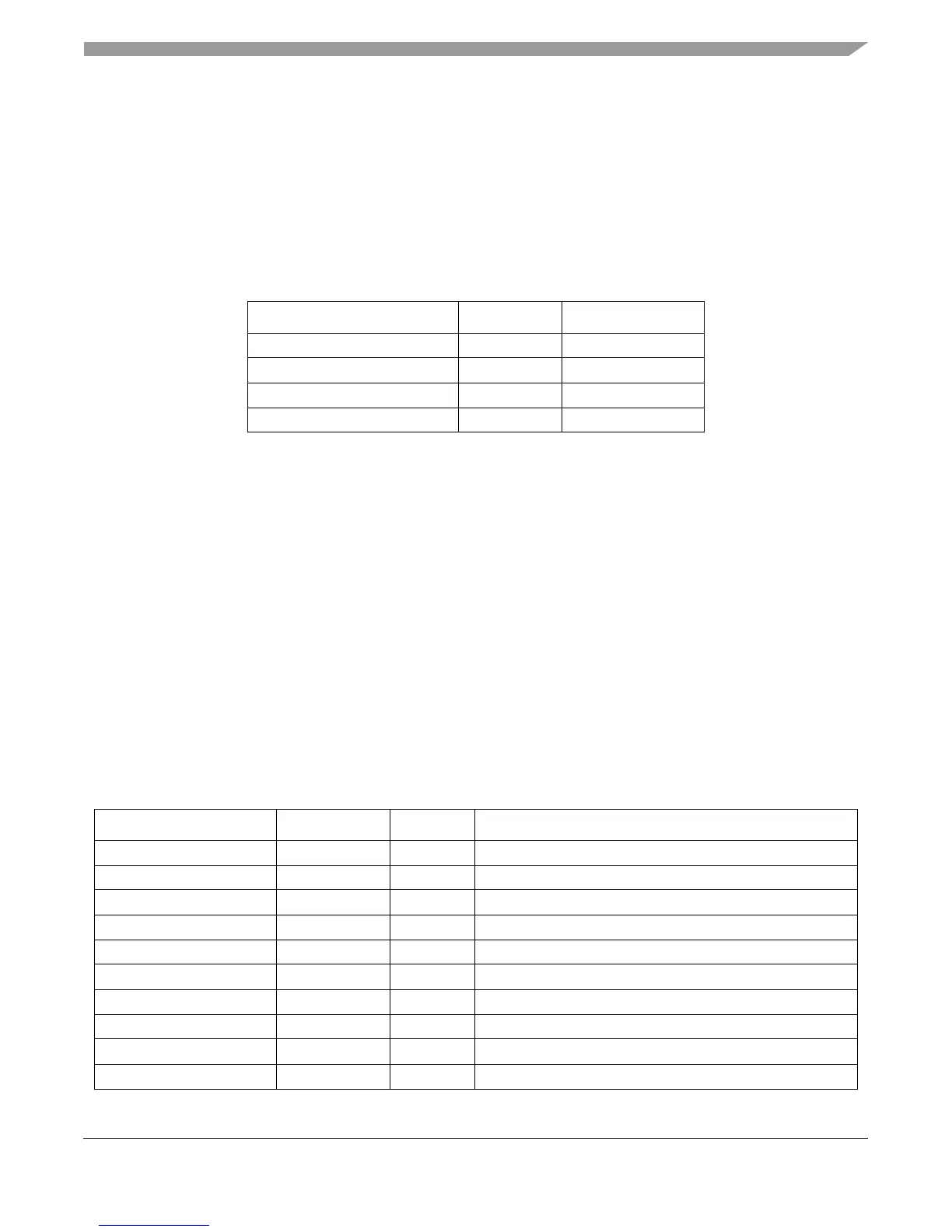

3.3.1.1.3 Integer Logical Instructions

The logical instructions shown in Table 3-8 perform bit-parallel operations on the specified

operands. Logical instructions with the CR updating enabled (uses dot suffix) and instructions

andi. and andis. set CR field CR0 to characterize the result of the logical operation. Logical

instructions do not affect XER[SO], XER[OV], or XER[CA].

See Appendix C, “Simplified Mnemonics for PowerPC Instructions,” for simplified mnemonic

examples for integer logical operations.

Table 3-7. Integer 32-Bit Compare Instructions (L = 0)

Name Mnemonic Syntax

Compare cmp crD,L,rA,rB

Compare Immediate cmpi crD,L,rA,SIMM

Compare Logical cmpl crD,L,rA,rB

Compare Logical Immediate cmpli crD,L,rA,UIMM

Table 3-8. Integer Logical Instructions

Name Mnemonic Syntax Implementation Notes

AND and (and.) rA,rS,rB—

AND Immediate andi. rA,rS,UIMM —

AND Immediate Shifted andis. rA,rS,UIMM —

AND with Complement andc (andc.) rA,rS,rB—

Count Leading Zeros Word cntlzw (cntlzw.) rA,rS—

Equivalent eqv (eqv.) rA,rS,rB—

Extend Sign Byte extsb (extsb.) rA,rS—

Extend Sign Half Word extsh (extsh.) rA,rS—

NAND nand (nand.) rA,rS,rB—

NOR nor (nor.) rA,rS,rB—

Loading...

Loading...